D-тригеры.

Устройства последовательностного типа, имеющие вход D информация с которого переписывается на выход тригера только по сигналу синхронизации С. D-триггер может быть только синхронным, имеет один информационный вход и вход С для подачи синхро импульсов.

Схема!!!!!!!!

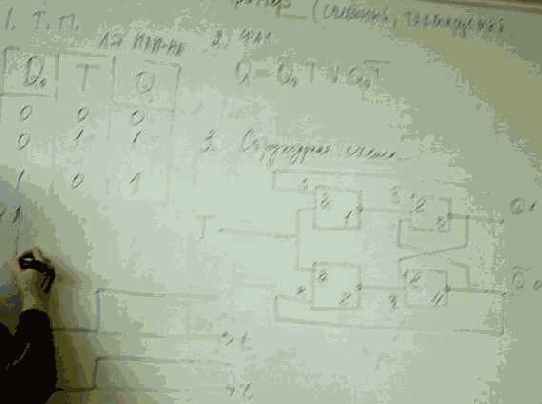

Таблица выходов D-тригера:

Структурная схема:

Условное обозначение:

VD-тригер.

Триггер с разрешающим входом V. При V равном 1 VD тригер работает как синхронный D тригер. При V=0

Он хранит предыдущее состояние. Так как информация на выходе D тригера остается неизменной, до прихода очередного импульса синхронизации то D тригер называется тригером с запоминанием информации, или тригером с защелкой. В связи с задердкой прохождения входного сигнала на выход, до прихода импульса синхронизации D тригер называется тригером задержки.

Т-тригер.

Устройства последовательностного типа с одним(единственным) входом, на который поступают тактовые импульсы.

Каждый тактовый импульс меняет состояние тригера на инверсное.

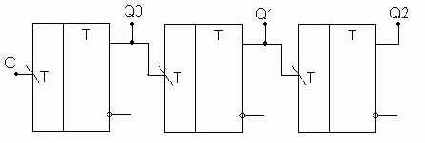

Одноступенчатые Т тригеры.

По определению Т тригер меняет свое сост ояние на инверсное по каждому активному сигналу действующему на информационном входе.

Реализация заданного режима работы, требует подачи на тригер для каждого последующего переключения инверсных значений.

Из ФАЛ следует что для реализации заданного режима работы необходимо подавать на вход триггера, при каждом последующем переключении инверсные значения. Такой режим может быть реализован путем введения в схему синхронного RS тригера.

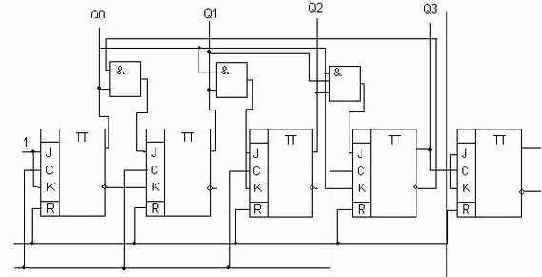

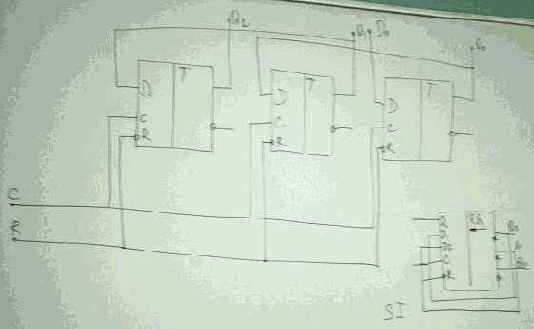

Двоично-десятичные счетчики.

В двоично-десятичном счетчике, модуль счета ведется до М=10. Каждый десятичный разряд счетчика является двоичным счетчиком с периодом цикла N=10, и называется декада. Десятичные счетчики используются в случае если необходимое число поступающих импульсов представлять в десятичной системе счисления. Каждый десятичный разряд счетчика называется декадой. Декада - это двоичный счетчик с периодом цикла N=10.

1 декада 2 декада

Схема построена по методу исключения лишних состояний. Каждая разрядная схема содержит триггер(JK триггер со статическим управлением) и логический элемент И формирующий сигнал переноса. Переключение триггеров осуществляется сигналом синхронизации С. Счетчик состоит из нескольких декад (двух). Первая декада считает единицы, вторая десятки и так далее. Триггер нулевой разрядной схемы каждой декады, реализует режим работы асинхронного JK триггера на синхронном JK триггере. Триггеры первой декады управляются импульсами сформированными на выходе предыдущей разрядной схемы. Управляющими импульсами следующей декады, является импульс с выхода старшей разрядной схемы предыдущей декады. Для данной схемы в момент отрицательного фронта десятого импульса, триггеры первой декады переходят в нулевое состояние.На выходе триггера 3(старшего) разряда сигнал логической единицы на ноль, что вызывает переход следующей декады в состояние соответствующему двоичному числу на единицу больше.

Двоично-кодированные счетчики.

Счетчики модуль счета, которых рассчитывается по формуле M=2 в степени N где Nне равно целому числу. Одним из распространенных счетчиков является счетчик двоично-десятичный. Модуль счета = 10. При построении двоично-кодированных счетчиков, получили распространение 2 способа: 1-метод исключения лишних состояний. 2-метод управляемого сброса.

Метод исключения лишних состояний – основан на методике синтеза последовательных устройств, где в схеме однозначно определяются виды связей между различными элементами. Такая схема не может быть оперативно изменена. Любое изменение требует перепроектирования в полном объеме. Метод используется только при проектировании часто используемых устройств выпускаемых большими партиями.

Метод управляемого сброса – принудительное формирование сигнала сброса триггеров в разрядных схемах счетчика, при появлении на выходе кода совпадающего с кодом требуемого модуля счета. Обнуление триггеров разрядных схем происходит по сигналу на основном логическом элементе (И) при приходе сигналов с выходов триггеров, соответствующих заданному модулю счета. После формирования активного уовня на выходе И и поступления сигнала на входы сброса триггера R на выходе триггера формируется код. Изменение алгоритма работы можно осуществить, если использовать возможность предварительной асинхронной установки исходного состояния.

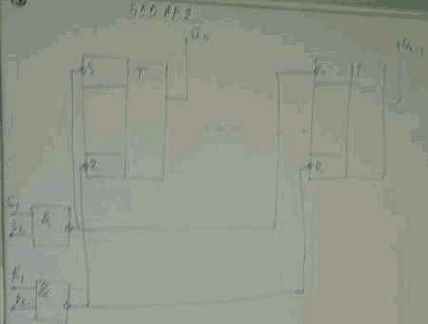

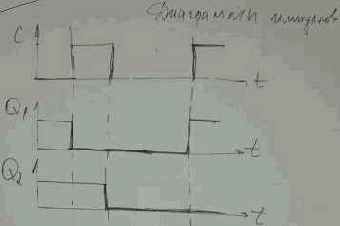

Двоичнодесятичный счетчик построеный методом управляемого сброса.

Построим на основе счетчика со сквозным переносом.

Со сквозным переносом двоичный

Метод управляемого сброса, заключается в формировании активного логического уровня при установлении на выходах счетчика кода соответствующего требуемому модулю счета и подачи от этого активного уровня на вход сброса асинхронной установки триггера, для обнуления разрядных схем счетчика. Активный уровень формируется на дополнительном логическом элементе И при поступлении на его входы требуемого кода. Например в двоично-десятичном счетчике соотв. код 1010 на выходах разрядных схем. Следовательно по приходе следующего кода 1010 должны быть установлены в нулевое состояние. Данный код поступая на вход логического элемента И-Не формирует уровень логического нуля на выходе что является активным логическим уровнем для инверсного входа R триггеров.

При использовании метода управляемого сброса, по импульсу при котором счетчик обнуляется на выходах триггеров формируется лишнее состояние(соответствующее коду обнуления) Если по условию работы счетчика формирование лишнего состояния недопустимо(даже кратковременное),то обнуление нужно проводить по последнему коду соответствующему модулю счета. Диаграммы импульсов двоично-десятичного счетчика реализующего метод управляемого сброса.

Если требуется получить выходной код в десятичной системе счисления то выходные сигналы с триггеров разрядных схем подключаются ко входу дешифратора.

Кольцевой счетчик используется для замены дешифратора, при необходимости осуществления подключения какого либо сигнала с выхода устройства к определенному входу.

График!

Делители частоты импульсной последовательности.

Устройства последовательностного типа которое при подачи на его входы периодической последовательности импульсов, формирует на выходе такую же последовательность импульсов но с частотой повторения сигналов в несколько раз меньше чем входная. В делителе частоты последовательности импульсов может быть произвольной, последовательность кодов, характеризующих последовательность импульсов в отличии от счетчика, где последовательность импульсов(бит-кода), определяет количество импульсов, поступивших на вход счетчика.

Так как последовательность импульсов делителей частоты может быть произвольной, то она выбирается из соображений обеспечения пи заданном цикле наибольшей простоты меж регирстровых связей. Счетчик может выполнять роль делителя частоты, но пи большом числе разрядных схем это экономически не целесообразно. Частота следования импульсов на выходе в 2 раза меньше чем на входе. Если последовательно соединить несколько делителей частоты, то на выходе первого частота импульсов будет в 2 раза реже второго, на выходе второго делителя частота будет в 2 раза реже чем на входе, на выходе 3 на выходе в 2 раза реже.

Делитель частоты с коэффициентом деления 3.

Счетчик с периодом цикла n=3 имеет простейшие меж разрядные связи и может служить делителем частоты с коэффициентом n=5.

В тех случаях коэффициент деления не является простым числом он может быть представлен в виде сомножеств коэффициентов деления с простым числом. Напрмер n=6 2*3/

Таким образом схемы соединяются последовательно образуя требуемый коэффициент деления.

Запоминающие устройства – это узлы вычислительного устройства для хранения информации.

Двоичные счетчики.

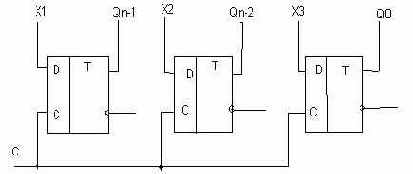

Двоичные счетчики с последовательным переносом.

Рассмотрим построение счетчика на примере двоичного трехразрядного регистра.

| С | Q1 Q2 Q3 |

| 1

1 1 1 1 1 1 1 |

0 0 0

0 0 1                                   1 1 0    |

|

Из таблицы переходов следует что переключение нулевой разрядной схемы Q0, происходит по каждому активному импульсу синхронизации. Переключение Q1 по каждому второму импульсу синхронизации переключение Q2 по каждому четвертому.

Переключение разрядной схемы происходит по импульсу синхронизации который следует за импульсом синхронизации, при котором все предыдущие разрядные схемы были установлены в единичное состояние.

Из таблицы переходов и диаграмм следует, что для того что бы построить вычитающий счетчик, вместо инверсного динамического входа Т триггера надо использовать прямой динамический, так как изменение сигнала на выходе, должно происходить по фронту импульса на входе, то есть изменение направление счета осуществляется путем изменения вида меж разрядных связей. При использовании комбинационной схемы позволяющей выбрать вид входного сигнала, можно построить реверсивный счетчик.

В суммирующем счетчике, для синхронизации последующих разрядных схем использовался сигнал с прямого выхода триггера, предыдущей разрядной схемы. Если использовать инверсный выход синхронизации, то суммирующий счетчик получится при подаче сигнала на прямой динамический вход.

Счетчики с последовательным переносом:

Счетчики с последовательным переносом реализуется простейшая схема построения счетчика. Недостатком является большое время установления выходного кода. И зависимость длительности установления выходного кода от вида самого кода.

Двоичные счетчики с параллельным переносом

Tk max = N*tkтр

N-число триггеров разрядных схем

Tkтр – время установления выходного сигнала на выходе триггера

Для этого необходимо вместо синхронных использовать асинхронные триггеры, управляемые сигналом синхронизации, которые обеспечат требуемый порядок переключения триггеров разрядных схем. Из таблиц переходов следует, что переключение разрядной схемы происходит после перехода импульса синхронизации только тогда, когда все триггеры предыдущих разрядных схем установлены то есть на выходах сигнал логической единицы.

Для одновременного переключения триггеров разрядных схем, необходимо сформировать сигнал переноса.

Так как в нулевой разрядной схеме сигнал переноса не учитывается, то Т триггер остался асинхронным, для обеспечения нормальной работы на вход Т подают сигнал логической единицы, время установления выходного кода, будет равно времени переключения одного триггера. Для нормальной работы, требуется некоторое время подготовки триггера для возможности учитывания сигнала переноса, при последующем переключении. Время подготовки определяется временем прохождения сигналов через логический элемент И.

Счетчик реализует операцию суммирования так как ко входе с триггера следующей разрядной схемы подключается выход предыдущей.

Выполняется операция вычитания так как к прямому входу подключается инверсный выход с триггера предыдущей разрядной схемы.

+реверсивный счетчик на JK триггерах. Смотри дальше. ->

Двоичные счетчики с комбинированным переносом.

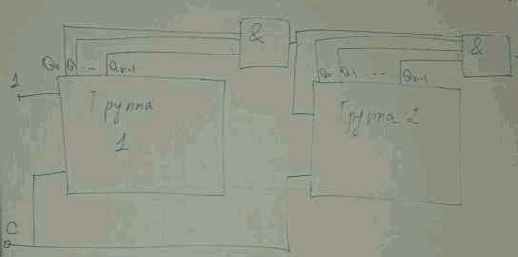

При большом числе разрядных схем в счетчике используется схема с комбинированным переносом, принцип которого состоит в разбиении общего числа разрядных схем на группы. Внутри группы, перенос учитывается либо по последовательному либо по параллельному принципу, между группами сигнал переноса учитывается только по параллельному принципу. Счетчики с комбинированным переносом соответственно могут быть: счетчики с последовательно параллельным переносом и с параллельно параллельным переносом.

Структурная схема счетчика с комбинированным переносом.

Время установления выходного кода будет равно tk max= tk гр

Tk гр-время установления выходного кода в пределах одной группы

Если в группе реализуется последовательный перенос, то время установления в группе равно tk гр=Nтр*tk тр

В частном случае каждая группа может содержать по одной разрядной схеме(триггеру) этом случае схема с комбинированным переносом в схему счетчика со сквозным переносом.

В схеме переключение разрядных схем происходит одновременно. Для подготовки к следующему переключению необходимо время для последовательного формирования на выходах всех элементах И новых значений. Время формирования сигнала зависит от вида кода записанного в счетчик. Получаемый выигрыш в быстродействии получается за счет того, что сигнал формируется на логических элементах И а не на триггерах.

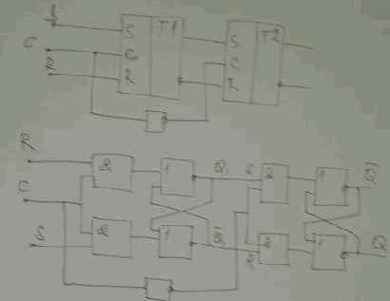

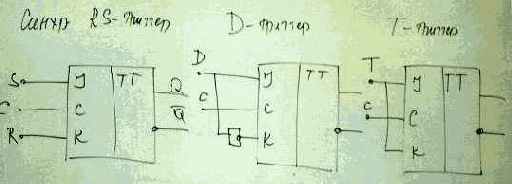

Двухступенчатый D-тригер

Двухступенчатый D-тригер с запрещающими связями между отдельными ступенями.

Двухступенчатый Т-тригер.

Выходные сигналы в двухступенчатом Т тригере задерживаются на время тактового

Выходные сигналы формируются на выходе выходной ступени тлько после перехода второй ступени в режим хранения когда сигналы поступающие по цепи пост не оказывают влияние на формирование выходных сигналов первой ступени.

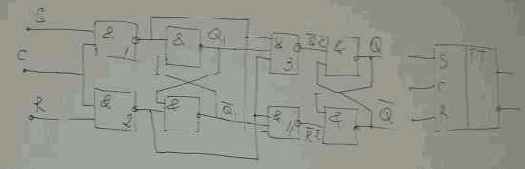

Двухступенчатый тригер.

MS тригеры – тригеры содержащие 2 тригерные структуры: 1-ведущий тригер(Master) 2-ведомый тригер(Slave). Синхронные тригеры со статическим управлением. Общая схема тригера с двухстпенчатым запоминанием информации.

Если С=1 ведущий тригер устанавливается в состояние соответствующие входным информационным сигналам. Ведомый тригер находится в режиме хранения так как на его вход поступает поступает сигнал С=0 так как на входе инвертор. При изменгении сигнала С с 1 на 0 ведущий тригер отключается от восприятия входных информационных сигналов, ведомый тригер переписывает сигналы сформированные на выходах ведущего тригера и формирует новый выходные сигналы. Таким образом, управление процессами в тригере с двухступенчатым запоминанием информации, за время тактового периода, осуществляется двумя фронтами сигнала синхронизации С.

На элементах или-не

На элементах и-не

Иерархическая структура памяти.

Очень часто, основные параметры запоминающих устройств находятся в противоречии, например большая емкость не сочитается с быстродействием. В следствие этого ЗУ свойственна много ступенчатая иерархическая структура, определяемая назначением устройства.

Регистровые ЗУ – находятся в составе процессора или других устройств(являются внутренними для этих устройств), благодаря которым уменьшается число обращений к другим уровням памяти, находящимся вне этих устройств.

КЭШ память – служит для хранения копий информации используемой в текущих операциях обмена, имеет высокое быстродействие.

Основная память – оперативная, постоянная, полупостоянная. Работает в режиме непосредственного обмена информацией с процессором и должна быть с ним по возможности максимально согласована с ним по быстродействию. В основной памяти хранится вся информация выполняемая в данный момент.

Специализированные виды памяти – (видео карта, мультипортовые и т.д.)

Внешняя память – служит для хранения больших объемов информации, реализована вне устройства ВТ, строится обычно на основе устройств с подвижным носителем информации.

Основные характеристики ЗУ:

1-информационная емкость – максимально возможный объем хранимой информации, выражается в битах или словах. Для хранения бита информации используется запоминающий элемент, для хранения слова или байта, используется запоминающая ячейка. ЗЯ содержит группу ЗМ , к которым возможно только одновременное обращение.

2-организация ЗУ – произведение числа хранимых слов на их разрядность M=N*R При одной и той же информационной емкости организация может быть различной.

3-быстродействие(производительность) – определяется временами считывания и записи информации и длительностями цикла чтения-записи. Время считывания – интервал между моментами появления сигнала чтения и слова на выходе. Время записи – интервал времени после появления сигнала записи достаточный для установления ЗЯ в состояния задаваемое входным словом. Цикл чтения-записи – минимально допустимый интервал времени между последовательными чтениями и записями. Длительности циклов могут превышать времена чтения или записи так как после этих операций может потребоваться время для восстановления начального состояния ЗУ. При сложном цикле обращений к хранимой информации процесс делится на 2 этапа: 1-время доступа при первом обращении (Latency) 2-темп передач последующих слов пакета (Bandwdth). Темп передач делится на 2 категории: 1-предельный 2-усредненный.

Классификация ЗУ.

Полупроводниковые ЗУ:

1-Адресные ЗУ делятся на 2 группы (ROM RAM) ROM – ROM(M),PROM,EPROM,EEPROM,FLASH. RAM – статические(асинхронные,тактируемые, синхронные(конвеерные)) динамические(стандартные, повышенного быстродействия, квазистатические)

2-Последовательные

3-Ассоциативные

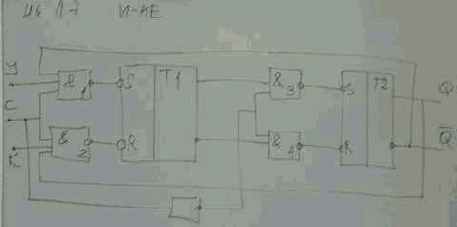

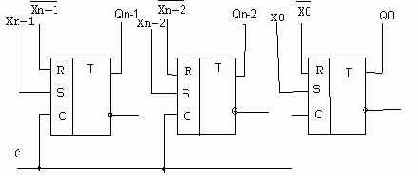

JK-триггеры.

При Т=1 К=1 триггер меняет свое состояние на инверсное.

Универсальные триггеры на основе JK-триггеров могут быть построены любые типы триггеров. JK-триггеры не имеют запрещенных наборов. JK-тригеры строятся на основе RS триггеров, путем создания инверсного режима при запрещенной комбинации входных сигналов. J-вход установки в состояние 1 К-вход сброса на ноль.

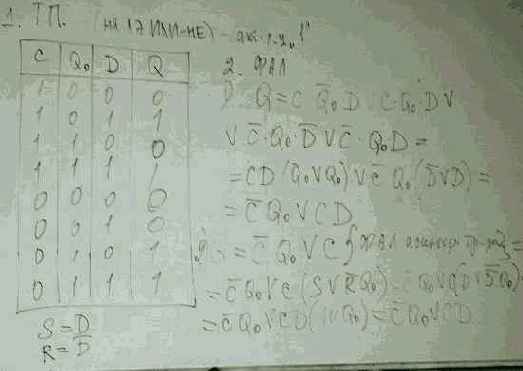

ФАЛ и таблица истинности

Таблица переходов, отображает определение входов J и K который при подаче на них активных логических уровней соответственно устанавливают и сбрасывают JK триггер, то есть входы J и K работают всегда с активными уровнями. Из ФАЛ следует, что при подаче на входы J и K двух активных уровней, JK триггер работает как счетный: выходное состояние тригера меняется при каждом импульсе синхронизации на инверсное. Следовательно JK триггер дожен иметь цепи ОС. Структура JK-триггера базируется на принципе построения триггера с двухступенчатым запоминанием информации или триггера с динамическим управлением.

Принцип работы: на входах трехвходового логического элемента И-НЕ 1,2 всегда будет присутствовать на одном лементе активный сигнал, на другом пассивный,так как по цепи обратной положительной связи, с выходов триггеров на входы логических элементов 1,2 поступают взаимо инверсные сигналы, следовательно на входах асинхронного RS триггера первой ступени не могут появиться 2 активных сигнала. Триггер работает по принципу двухступенчатого запоминания информации: при активном сигнале синхронизации С информация переписывается в Т1, Т2 находится в режиме хранения. При пассивном уровне сигнала синхронизации C информация с Т1 переписывается на Т2. JK-триггеры могут быть дополнениы входами асинхронной установки, которые имеют наивысший приоритет.

Классификация регистров.

Регистры классифицируются:

1-по способу обмена информацией: 1)параллельные(статические) информация записывается и считывается только в параллельной форме 2) последовательные(сдвигающие) информация записывается и считывается только в последовательной форме 3) последовательнопараллельные информация записывается и в параллельной и в последовательной ворме. И в посл. формах . 4)Парафазные информация записывается и считывается как в прямых так и в обратных кодах. 5)однофазные

3-по способу тактирования: 1)однотактные – управляемые одной управляющей последовательностью 2) много тактные – управляемые несколькими упавляющими последовательностями импульсов.

Параллельный регистр.

Параллельный регистр предназначен для выполнения микро операций установки в исходное состояние, ввод информации в параллельной форме, хранение информации и считывание информации в параллельной форме.

Простейший регистр может быть выполнен на RS или D –триггерах. Регистры содержат N триггеров, где N –ь число разрядных схем регистров. В соответствии с классификацией, в зависимости от использованных входов и выходов, регистры могут обозначаться как регистры на D-триггерах – однотактный, однофазный регистр с прямыми входами и выходами. Регистр на RS триггерах – однотактный регистр с парафазными входами и однофазным прямым выходом. Регистр на RS триггерах, содержит n триггеров, в которых входы синхронизации объединены между собой. На входы информация подается в прямом и обратном кодах. А с выхода снимаются только в прямом коде. Если в регистре используется для записи информации только прямой или обратный код, то запись информации выполняется за 2 такта синхронизации: по первому такту необходимо сбросить или установить все триггеры по второму записать новую информацию. При использовании D-триггеров запись информации будет производится быстрее, так как для записи информации необходим только один импульс синхронизации.

Регистр ИС 555ИР15 конспект лекции.

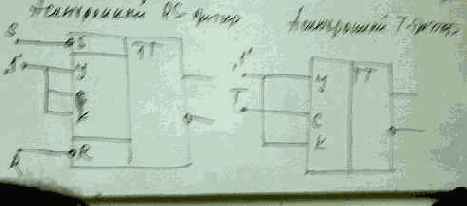

RS тригер с запрещающими связями между отдельными элементами.

Такой режим работы исключает одновременную подачу 2 активных уровней на ведомые тригеры, и заменяет инверсный сигнал синхронизации схемотехническим решением.

При С равном единице, в процессе записи информации в тригер Т1 на выходе одного из логических элементов 1 или 2 формируется сигнал логического нуля. Поэтому ЛЭ 3,4 будут заданы, и ведомый тригер Т2 будет находиться в режиме хранения информации. При С=0 на логических элементах 1 и2 формируется сигнал логической единицы, который является пассивным для тригера на элементах И-НЕ. Таким образом ведущий тригер Т1 переходит в режим хранения информации. На логические элементы 3,4 будет поступать сигнал логической единицы, который обеспечит переписывание выходных сигналов Т1 на входы ЛЭ 3,4 и Т2, то есть, происходит формирование выходных сигналов двухступенчатого тригера.

Вывод: запись информации в двухступенчатые тригеры, происходит по срезу входного импульса, то есть с задержкой на длительность синхроимпульса. Это свойство позволило создать Т и JK тригеры.

Схема записи информации в двух направлениях.

Используя различные комбинации, можно разработать разрядные схемы реализующие необходимый алгоритм работы. Одной из распространенных схем является схема записи информации в двух направлениях.

При С1=1 С2=0 В триггер разрядной схемы будет записано значение сигнала Х При С1=0 С2=1 значение Y.

Последовательный регистр: выполняет операцию записи информации в последовательной форме, хранение информации, считывание информации в последовательной форме и сдвига информации. Запись информаци от младшего разряда к старшему, осуществляется по первому такту синхронизации записывается значение старшего разряда. Полностью значение всех разрядных схем вводится за N тактов синхронизации, где N – число разрядных схем.

Запись информации от старших к младшим. То сдвиг информации слева на вправо. Запись осуществляется вводом сигнала в старшую разрядную схему, значение сигнала должно соответствовать значению нулевого разряда.

Регистр в котором реализуется запись двух направлений, то есть от младших к старшим и от младших к старшим, называется реверсивным.

Универсальный сдвиговый регистр:

Сдвигающие регистры являются как правило универсальными и могут выполнять все доступные для регистров микро операции. Для этого разрядные схемы входящие в состав регистра должны быть соединены между собой и иметь возможность загрузки информации в параллельной форме.

Выбор режима работы регистра осуществляется значением сигнала на входе S/P. При S/P=0 элемент DD1 формирует на своем выходе сигнал логической единицы, независимо от сигнала синхронизации С, так как управление режимом последовательной записи в триггер осуществляется инверсным сигналом синхронизации, то в этом случае сигнал логической единицы блокирует режим последовательного ввода информации(синхронное переключение триггера). Элементы DD3 и DD5 преобразуются в инверторы и сигналы присутствующие на входах параллельной записи информации D переписываются в триггеры разрядных схем, то есть осуществляется режим параллельной записи информации, элементы DD4 и DD6 работают как инверторы(от сигнала S/P=0 на вход DD2 поступает на вх…..)……..

Направление сдвига в реверсивном регистре определяется управляющим сигналом. Схемотехнически такой регистр может быть построен на D-триггерах, путем ввода дополнительного элемента выбора.

При S=1 на выходе логического элемента &1 сигнал будет определятся входным сигналом V. На выходе логического элемента &2 будет формироваться сигнал логического нуля, так как на один из входов &2 поступает сигнал с инвертора. Таким образом при S=1 формируется один из сигналов поступающий на вход разрядной схемы триггеров с выхода младшей разрядной схемы. При S=0 в триггер будет переписываться информация с элемента &2 , то есть, будет реализован сдвиг информации слева на право от старших к младшим.

Организация межрегистровых связей.

Организация индивидуальной связи- реализует пространственное разделение цепи передачи информации, при этом обмен информацией между несколькими регистрами может происходить одновременно. Это обеспечивает максимальное быстродействие устройства. Недостаток- при большом числе регистров возникают технические сложности проектирования и изготовления индивидуальных линий соединения.

Организация обмена информации по одной линии связи. Этот способ основан на обмене информацией между регистрами по последовательному принципу. Используется одна линия связи – общая шина. К шине подключаются входы и выходы всех регистров, обмен информацией между двумя регистрами осуществляется в строго определенный момент времени, остальные регистры от обмена информацией отключены. Такая схема используется в микропроцессорных системах, путь передачи информации, определяется управляющими сигналами.

Параллельное соединение нескольких входов и выходов различных регистров только при наличии в схеме дополнительных элементов, определяющих путь передачи информации. В статическом регистре К555ИР15 используются DD6 разрешающие запись информации только при подаче соответствующего сигнала на входы Е1 иллли Е2 на входы Z элементов DD8 которые соединяют выходы триггеров разрядных схем с выводами микросхемы, только при наличии управляющего сигнала EZ1 или EZ2

Счетчики – последовательные устройства, предназначенные для счета входных импульсов и фиксации их числа в двоичном коде. Счетчики строятся на основе однотипных разрядных схем связанных между собой. Разрядная схема состоит из триггера и комбинационной схемы управления триггером.

Основные параметры:

1-основной статический параметр- модуль счета М- характеризует максимальное число импульсов, после прихода которых счетчик устанавливается в исходное состояние.

2-основний динамический параметр – время установления выходного кода – определяет быстродействие счетчика, характеризуется временным интервалом между моментом подачи входного сигнала и установлением нового кода на выходе.

Микрооперации выполняемые счетчиками.

1-установка в исходное состояние( запись нулевого кода)

2-запись входной информации в параллельной форме

3-хранение информации

4-считывание информации в параллельной форме.

5-инкремент(увеличение кода на 1)

6-декремент(уменьшение кода на 1)

Классификация:

По значению модуля счета – двоичные и

По направлению счета – суммирующие, вычитающие, реверсивные.

По способу передачи параллельные и

Триггеры построенные на основе JK-триггеров.

На базе JK–триггеров могут быть построены все рассмотренные ранее триггеры.

Триггеры с динамическим управлением.

Все предыдущие рассмотренные типы триггеров являлись триггерами со статическим управлением, то есть при С=1 в течение всего интервала длительности триггером воспринимается любое изменение входных информационыых сигналов. Для того что бы сформировать единичный импульс на выходе, необходимо что бы в течение всего промежутка времени С=1 входные информационные сигналы не менялись.

От этого недостатка свободны триггеры с динамическим управлением. Суть динамического управления заключается в том, что в качестве активного динамического сигнала, используется не статический уровень( С=константа) а его изменение, то есть переключение триггера происходит в начальный момент при переходе сигнала управления С из логического нуля в единицу, или из логической единицы в ноль. Если тригер переключается при переходе от нуля к единице(в начале фронта импульса) то считается что триггер снабжен прямым динамическим входом. Если переключение происходит в начальный момент при переходе из единицы в ноль(по срезу импульса) то считается что триггер снабжен инверсным динамическим входом.

Схема с динамическим управлением реализуется подачей информационных сигналов на основную ячейку памяти(асинхронный RS триггер не через вспомогательную комбинационную схему(схему синхронизации на ЛЭ) а на дополнительные элементы памяти(асинхронные RS триггеры.

Так как асинхронный RS триггер имеет 2 входа( R и S) то необходимо 2 вспомогательных RS триггера. Такая схема называется схемой 3-х триггеров.

Рис-схема 1!!!!!!!!!!

Элементы 1 и 2 образуют асинхронный RS триггер на логических элементах ИЛИ-НЕ состояние схемы определяется информационным сигналом D. Выходная триггерная RS структура переключается сигналами Y1 и Y2 , которые формируют логические элементы И-НЕ 3-6, на положительном фронте С на выходе устанавливается сигнал определяемый D.

В разрядном триггере есть элемент памяти и комбинационный элемент