Интерфейс клавиатуры

Традиционная клавиатура PC представляет собой унифицированное устройство ввода со стандартным разъемом и последовательным интерфейсом связи с системной платой. В настоящее время используются так называемые расширенные (enhanced) клавиатуры ATилн PS/2, имеющие более 100 клавиш. Они вытеснили первые 84-клавишные клавиатуры AT и тем более клавиатуры XT. По электрическому интерфейсу клавиатуры XT и AT совпадают, за исключением того, что двунаправленный интерфейс позволяет клавиатуре AT принимать команды от системной платы. Однако по логическому интерфейсу они несовместимы (клавиатура AT иногда имеет переключатель режима XT/AT). Клавиатура PS/2 отличается от AT только исполнением разъема, при необходимости можно использовать переходник.

Клавиатуры имеют внутренний микроконтроллер, способный определить факты нажатия и отпускания клавиш, при этом можно нажимать очередную клавишу, даже удерживая несколько ранее нажатых. При нажатии клавиши клавиатура передает идентифицирующий ее скан-код. При удержании клавиши в нажатом положении через некоторое время клавиатура начинает автоповтор передачи скан-кода нажатия этой клавиши. Задержка автоповтора (typematic delay) и скорость автоповтора (typematic rate) для клавиатур AT программируются. Расширенная клавиатура позволяет выбирать 1 из 3 наборов скан-кодов.

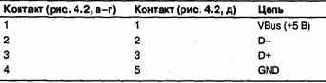

С распространением шины USB появились клавиатуры и с этим интерфейсом; они имеют и встроенный хаб, например для подключения мыши USB. Клавиатура USB питается от шины. Для клавиатуры USB требуется специальная поддержка со стороны BIOS; она имеется в современных системных платах.

8.1. Интерфейс клавиатуры.___________________________________________ 311

Для подключения клавиатуры предназначен последовательный

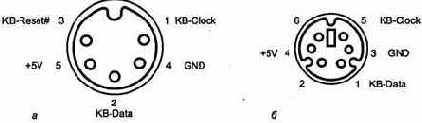

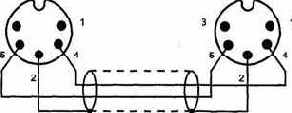

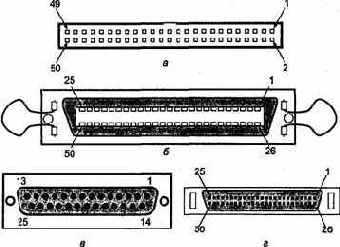

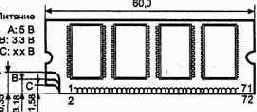

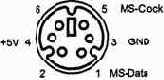

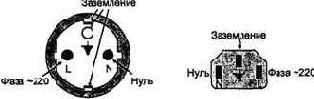

Для подключения клавиатуры предназначен последовательный синхронный двунаправленный интерфейс, состоящий из двух обязательных сигналов KB-Data и KB-Clock. Обе линии на системной плате подтягиваются резисторами к шине +5 В. На обеих сторонах интерфейса выходные сигналы низкого уровня формируются выходами элементов с открытым коллектором (стоком), а состояние линий может быть прочитано через входные линии контроллеров. Вид разъемов (со стороны задней панели) и назначение контактов приведены на рис. 8.1. Конструктивно возможны два варианта разъема — обычная 5-контактная розетка DIN (клавиатура AT) или малогабаритная розетка mini-DIN (PS/2). На этот же разъем через плавкий предохранитель поступает напряжение питания клавиатуры +5 В.

Рис. 8.1. Разъемы (вид со стороны контактов) подключения клавиатур: а — AT и б — PS/2

ВНИМАНИЕ---------------------------------------------------------------------------------

Питание от разъема клавиатуры часто используется такими устройствами, как внешние накопители или адаптеры локальных сетей, подключаемыми к параллельному порту. Плавкий предохранитель, установленный на системной плате, может не выдержать броска тока, потребляемого этими устройствами. При этом откажется работать и клавиатура — ее индикаторы даже и не мигнут при включении.

Контроллер транслирует команды в посылки, направляемые к клавиатуре.

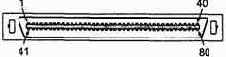

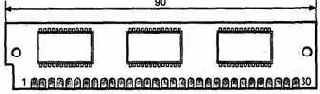

Работу двунаправленного интерфейса иллюстрирует рис. 8.2, а, где серым цветом помечены сигналы, формируемые контроллером, а черным — клавиатурой. В исходном состоянии обе линии «отпущены» выходными формирователями в состояние с высоким уровнем. Клавиатура может начать передачу данных в произволь-

312_________ Глава 8. Специализированные интерфейсы периферийных устройств

ный момент, когда интерфейс находится в покое. Клавиатура формирует стартовый бит (низкий уровень) на линии KB-Data и первый импульс KB-Clock, что является сигналом контроллеру о необходимости начала приема. После подъема KB-Clock она выводит 0-й бит данных на линию KB-Data, а затем и следующий импульс KB-Clock. Контроллер должен «защелкивать» принятый бит данных по спаду KB-Clock. Так передаются все 8 бит данных и бит паритета, дополняющий число единичных бит до нечетного. После синхроимпульса бита паритета контроллер клавиатуры должен сформировать импульс KB-Clock, подтверждающий прием байта (Ack). Если весь байт с битом паритета не будет получен контроллером за 2 мс, контроллер прекращает прием данного байта и фиксирует ошибку тайм-аута.

Рис. 8.2. Временные диаграммы интерфейса клавиатуры: а — прием посылки от клавиатуры,

б — передача команды в клавиатуру

Обратная передача — вывод команды контроллера в клавиатуру — происходит несколько сложнее (рис. 8.2, б). Из состояния покоя контроллер устанавливает низкий уровень KB-Clock на 250 мкс и формирует старт-бит (низкий уровень) — это сигнал клавиатуре на прием команды. На него клавиатура должна ответить серией из 11 импульсов KB-Clock. По спаду очередного синхроимпульса контроллер выставляет очередной бит данных, а клавиатура его «защелкивает» по фронту формируемого ею же синхроимпульса. После бита паритета (9-й импульс) и единичного стоп-бита (10-й) на 11-м импульсе клавиатура формирует нулевой бит подтверждения (Ack).

После этого контроллер формирует импульс KB-Clock (60 мкс), который является запросом на прием ответа клавиатуры. Контроллер ожидает окончания ответа на этот запрос не долее 20 мс и, если ответ не придет за это время, сформирует ошибку тайм-аута. Ошибка будет также в случае, если клавиатура не введет первый синхроимпульс за 15 мс от начала запроса или контроллер не примет данные, включая стоп-бит, за 2 мс с момента появления синхроимпульса бита 0.

На системной плате PC/XT контроллера 8042 не было, а интерфейс клавиатуры (однонаправленный) был реализован аппаратной логикой — регистром сдвига, параллельный выход которого подключается к входам порта А системного интерфейса 18255. По приему байта от клавиатуры вырабатывается аппаратное прерывание IRQ1, обработчик которого может прочитать принятый байт из порта 60h. С помощью бит 7 и 6 порта 61h возможны программная блокировка и сброс клавиатуры соответственно. Сброс клавиатуры XT осуществляется обнулением линии KB-Clock.

8.1. Интерфейс клавиатуры____________________________________________ 313

Интерфейс коммутируемой телефонной линии и телефонного аппарата

Коммутируемые линии (dial-up lines) являются наиболее распространенным внешним интерфейсом телефонной сети, к которому компьютер подключается с помощью модема. Эти линии являются аналоговыми, по одной двухпроводной линии передаются сигналы в обоих направлениях (прием и передача). Коммутируемые линии обеспечивают прохождение сигнала (речевого или данных через модем)

10.3. Интерфейс коммутируемой телефонной линии и телефонного аппарата 415

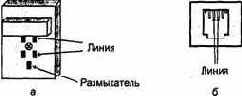

в полосе частот шириной 3,1 кГц (300-3400 Гц), а также поддерживают сигнализацию, принятую для аналоговой телефонии. Коммутируемые линии позволяют устанавливать временные соединения с любыми абонентами телефонной сети в пределах возможностей, предоставляемых АТС, к которой произведено подключение. В качестве соединителей при подключении абонента в нашей стране широко используются 4-контактные разъемы, изображенные на рис. 10.4, а. Для некоторых специфических случаев применения эти разъемы могут иметь размыкатели и дополнительный конденсатор. Как правило, используется только одна пара контактов. Сейчас их вытесняют соединители международного стандарта RJ-11 — 6-позици-онный модульный коннектор с четырьмя контактами, из которых задействуется только средняя пара (рис. 10.4, б).

ВНИМАНИЕ

Рис. 10.4. Розетки для телефонных линий: а —стандарт бывшего СЭВ, б — международный стандарт

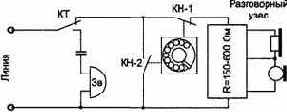

Упрощенная схема стандартной нагрузки линии — телефонного аппарата — приведена на рис. 10.5. В состоянии покоя (idle) аппаратура АТС посылает в линию напряжение постоянного тока 60 В через ограничительные резисторы с суммарным сопротивлением 700-1500 Ом и следит за током в линии.

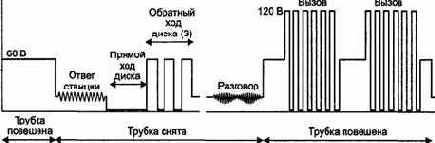

При опущенной трубке (on-hook) KT переключается и подключает через конденсатор вызывное устройство (Зв), при этом телефон не нагружает линию по постоянному току. Для вызова абонента АТС посылает серию импульсов амплитудой около 120 В с частотой 25 Гц. Эти импульсы через конденсатор проходят в обмотку звонка и вызывают колебания молоточка. При снятой трубке (off-hook) к линии подключается разговорный узел (это положение показано на рисунке), его сопротивление постоянному току — около 150-600 Ом. Разговорный узел содержит микрофон, телефон и схему подавления прослушивания сигнала собственного микрофона. Для предотвращения травм органов слуха предусмотрен ограничитель напряжения звукового сигнала. Подключение разговорного узла приводит к протеканию постоянного тока в линии, что позволяет станции фиксировать факт снятия трубки. При снятии трубки станция посылает непрерывный тональный сигнал ответа (425 Гц) и готовится принять сигналы набора номера. В это время (а также во время разго-

416

Глава 10. Интерфейсы компьютерных сетей

вора после установления соединения) на нагрузке телефона падение напряжения составляет около 5-15 В постоянного тока, и на фоне этого уровня переменная составляющая (звуковой сигнал разговора) имеет амплитуду порядка десятков-сотен милливольт. Отбой (вешание трубки, on-hook) сигнализируется разрывом цепи для постоянного тока. На данной схеме показаны цепи импульсного набора номера (pulse dialing). При наборе номера (трубка снята) разговорный узел отключается контактом КН-1. Во время «взвода» диска контакт КН-2 замыкается, во время обратного хода он п раз размыкается (по одному разрыву на единицу набираемой цифры, 0—10 разрывов). После окончания набора цифры контакты КН-1 снова подключают разговорный узел. Длительность (60 мс) и частота (10±1 имп/с) разрывов стандартизованы и рассчитаны на время срабатывания шаговых искателей «древних» станций. Импульсный набор ради совместимости со старыми телефонами поддерживается всеми АТС.

О результате коммутации станция сигнализирует короткими гудками «занято» (busy) — тональный сигнал 425 Гц, длительность посылки и паузы 0,35 с или длинными гудками (1с посылка, 3 с пауза), синхронными не всегда с сигналами, вызывающими абонента. Временная диаграмма сигналов на внешних контактах телефонного аппарата в разных стадиях показана на рис. 10.6.

Рис. 10.5. Упрощенная схема телефонного аппарата (трубка снята)

Рис. 10.6. Временная диаграмма работы телефонного аппарата с импульсным набором

При тональном наборе (tone dialing) каждая цифра кодируется парой из восьми тональных частот звукового диапазона, передаваемых телефоном в линию. Допустимы 16 комбинаций, которые позволяют кодировать 10 цифр и дополнитель-

10.3. Интерфейс коммутируемой телефонной линии и телефонного аппарата

417

ные символы (кнопки #, *) для получения дополнительных услуг от АТС. Тональный набор выполняется гораздо быстрее (один символ передается за 40 мс) и надежнее, но поддерживается еще не всеми АТС. Возможность тонального набора имеют большинство моделей «кнопочных» телефонов, но для совместимости со старыми АТС они позволяют переключаться на импульсный набор. Тональный набор позволяет вводить и дополнительные цифры для выбора одного из абонентов мини-АТС, подключенной к обычной телефонной линии. Дополнительные цифры набираются вызывающим абонентом после установления соединения с мини-АТС по обычному номеру, после специального приглашения автоответчика мини-АТС.

Для блокированных (спаренных) телефонов одна двухпроводная линия от АТС обслуживает двух абонентов с разными номерами поочередно. Для разделения линий используется пассивное устройство-блокиратор — два однополупериодных выпрямителя сигнала с линии от АТС. Здесь АТС задействует положительную полярность сигнала для работы с абонентом 1 и отрицательную — для работы с абонентом 2. Когда приходит внешний вызов, его сигнал станция посылает в полярности, соответствующей вызываемому абоненту.

Для опроса состояния (поднята/ опущена трубка) АТС чередует полярность опрашивающего напряжения с низкой частотой (этот рокот можно услышать, если в момент плавного снятия трубки контакты включения трубки сработают раньше, чем замыкающие контакты нагрузочного резистора). Как только обнаружена снятая трубка у одного из абонентов, станция останавливает чередование опроса на «его» полярности и работает вышеописанная сигнализация. Для спаривания телефонов применяют и частотное разделение: для одного из абонентов сигнал передается на высокой частоте (с модуляцией). Блокирование (спаривание) телефонов позволяет экономить физические линии, но имеет ряд очевидных неудобств: абоненты могут пользоваться телефонами лишь поочередно, «захватывая» линию на время до «отбоя». Для внешних звонков к абоненту линия представляется занятой как во время его разговора, так и во время разговора соседа. Сблокированные линии «не любят» некоторые модели модемов.

Для автоматического определения номера (АОН) вызывающего абонента имеется специальная система сигнализации, поддерживаемая большинством отечественных АТС. Ее работу иллюстрирует диаграмма, показанная на рис. 10.7. Когда телефон с АОН получает вызывной сигнал, он до подключения разговорного узла включает цепь, на которой падает напряжение около 24 В, и через 250-275 мс в линию посылает тональный сигнал «запрос». Этот сигнал должен иметь частоту 500 Гц и длительность 100 мс. В ответ на этот сигнал АТС передает несколько раз повторяющийся пакет из десяти двухчастотных посылок, в котором сообщается категория и 7-значный номер вызывающего абонента. Каждая посылка продолжается 40 мс и содержит две из шести возможных тональных частот (700,900,1100, 1300, 1500 и 1700 Гц). Таким образом кодируются цифры 0-9 и служебные символы «начало» и «повтор». Символ «начало» обрамляет пакет, символ «повтор» используется, если последующая цифра повторяет предыдущую (чтобы облегчить выделение посылок).

После приема ответа АОН может имитировать (для вызы-

418

Глава 10. Интерфейсы компьютерных сетей

вающего абонента) длинные гудки, в это время вызываемый абонент может решить, снимать трубку или нет, включить автоответчик и т. п. На время разговора (или работы автоответчика) включается РУ с обычным сопротивлением, и напряжение падает до 5-15 В. Отбой выполняется обычным образом. Для зарубежных АТС аналогом услуги АОН (которая первоначально не предназначалась для широкого круга пользователей) является услуга идентификации вызывающего абонента (Caller Id), предоставляемая только цифровыми станциями. Она работает по совсем иному протоколу.

Рис. 10.7. Последовательность сигналов при автоматическом определении номера

Современные кнопочные телефоны, а также модемы и факс-модемы отрабатывают телефонную сигнализацию по вышеописанной схеме. Коммутирующими элементами у них могут быть электронные ключи или малогабаритные реле (их щелчки на модемах хорошо слышны при работе), вместо электромагнитного звонка применяется электронный генератор сигнала, традиционный угольный микрофон может заменяться электретным с усилителем. Схемотехнически они могут заметно отличаться от вышеприведенной схемы, но всяко должны обеспечивать сопротивление постоянному току при повешенной трубке (и в момент прерывания при наборе номера) не менее 250 кОм, во время набора номера (в фазе замыкания) — не более 50 Ом.

Параметры сигналов зарубежных АТС и выпускаемых для них телефонов несколько отличаются от отечественных: номинальное напряжение — 40 В, вызывные импульсы — до 90 В, уровень звукового сигнала при разговоре ниже. Из-за этих различий, например, абонент отечественного телефона хуже слышит абонента импортного телефона, а абонент импортного телефона слышит первого лучше. Из-за слишком большой амплитуды вызывного напряжения (на некоторых АТС она может достигать 200 В) аппараты могут выходить из строя. Защита линии от перенапряжения с помощью стабилитронов или варисторов в этом случае не позволит дозвониться до «защищенного» абонента: при большой амплитуде импульсов ток потечет через ограничитель и станция зафиксирует это как снятие трубки.

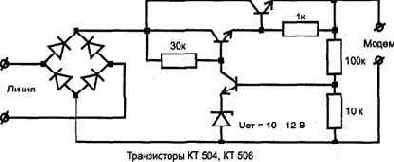

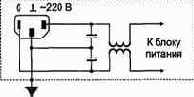

Далее подается обычное напряжение (ниже ограничения), ток прекращается и станция фиксирует отбой. Выходом в такой ситуации может быть применение схемы «стабилизатора вызывного напряжения» (рис. 10.8), с помощью которой автор сумел подключить модем с защитой от перенапряжений к линии от «ретивой»

10.3. Интерфейс коммутируемой телефонной линии и телефонного аппарата 419

АТС. Любопытным оказался факт, что ограничитель напряжения был спрятан в кабеле, прилагавшемся^ модему (с виду — обычный шнур с вилками RJ-11). Схема не претендует на оптимальность решения, но работает.

Рис. 10.8. Стабилизатор вызывного напряжения

На линиях отечественных АТС рекомендуется использовать оборудование, специально адаптированное для нашей страны (и сертифицированное Министерством связи).

Интерфейс LPC

Интерфейс LPC (Low Pin Count — малое число выводов) предназначен для локального подключения устройств, ранее использовавших шину X-Bus или ISA: контроллеров НГМД, последовательных и параллельных портов, клавиатуры, аудиокодека, BIOS и т. п. Введение нового интерфейса обусловлено изживанием шины ISA с ее большим числом сигналов и неудобной асинхронностью. Интерфейс обеспечивает те же циклы обращения, что и ISA: чтение-запись памяти и ввода-вывода, DMA и прямое управление шиной (bus mastering). Устройства могут вырабатывать запросы прерываний. В отличие от ISA/X-Bus с их 24-битной шиной адреса, обеспечивающей адресацию лишь в пределах первых 16 Мбайт памяти, интерфейс LPC имеет 32-битную адресацию памяти, что обеспечивает доступ к 4 Гбайт памяти. 16-битная адресация портов обеспечивает доступ ко всему пространству 64 К портов. Интерфейс синхронизирован с шиной PCI, но устройства могут вводить произвольное число тактов ожидания. Интерфейс программно прозрачен — как и для ISA/X-Bus, не требует каких-либо драйверов. Контроллер интерфейса LPC является устройством-мостом PCI. По пропускной способности интерфейс

224_____________________________________ Глава 6. Шины и карты расширения

практически эквивалентен этим шинам. В спецификации LPC 1.0 приводится расчет пропускной способности интерфейса и устройств, его использующих. При наличии буферов FIFO интерфейс наиболее выгодно использовать в режиме DMA. В этом случае главным потребителем будет LPT-порт — при скорости передачи данных 2 Мбайт/с он займет 47 % полосы интерфейса. Следующим будет инфракрасный порт — 4 Мбит/с (11,4 %). Остальным устройствам (контроллер НГМД, СОМ-порт, аудиокодек) требуются еще меньшие доли, в результате они занимают до 75 % полосы при одновременной работе. Таким образом, перевод этих устройств с ISA/X-Bus на LPC не должен вызывать проблем производительности более острых, чем были на старых шинах. Интерфейс имеет всего 7 обязательных сигналов:

¦ LAD[3:0] — двунаправленная мультиплексированная шина данных;

¦ LFRAME* — индикатор начала и конца цикла, управляемый хостом;

¦ LRESET# — сигнал сброса, тот же, что и RST# на шине PCI;

¦ LCLK — синхронизация (33 Мгц), тот же сигнал, что и CLK на шине PCI;

Дополнительные сигналы интерфейса LPC:

¦ LDRQ* — кодированный запрос DMA/Bus Master от периферии;

¦ SERIRQ — линия запросов прерывания (в последовательном коде), используется, если нет стандартных линий запросов IRQ в стиле ISA;

¦ CLKRUN* — сигнал, используемый для указания на остановку шины (в мобильных системах), требуется только для устройств, нуждающихся в DMA/BusMaster в системах, способных останавливать шину PCI;

¦ РМЕ# — событие системы управления потреблением (Power Management Event),может вводиться периферией, как и в PCI;

¦ LPCPD# — Power Down, указание от хоста устройствам на подготовку к вы

ключению питания;

¦ L.SMI* — запрос прерывания SMI# для повтора инструкции ввода-вывода.

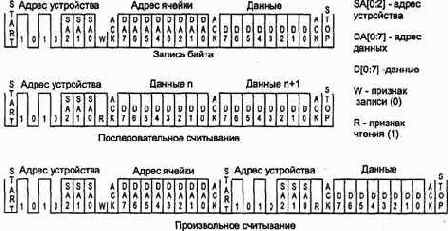

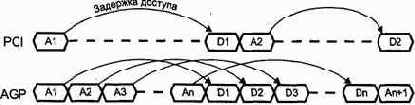

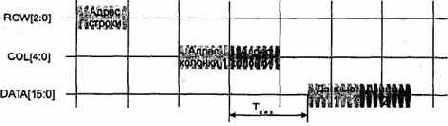

Сигналы LFRAME* и LAD[3:0] синхронизированы (являются действительными) по фронту LCLK. По шине LAD[3:0] в каждом такте цикла передаются поля элементов протокола. Обобщенная временная диаграмма цикла обмена по LPC приведена на рис. 6.15. Начало каждого цикла хост отмечает сигналом LFRAME*, помещая на шину LAD[3:0] поле START. По сигналу LFRAME* все ПУ должны прекратить управление шиной LAD[3:0], а по коду поля START они должны декодировать последующие события как цикл шины. В следующем такте хост снимет сигнал LFRAME* и поместит на шину LAD[3:0] код типа цикла CYCTYPE. Сигнал LFRAME# может длиться и более одного такта, но признаком начала цикла (поля START) является последний такт перед снятием сигнала. С помощью сигнала LFRAME* хост может принудительно прервать цикл (например, по ошибке тайм-аута), выставив соответствующий код.

3.4. Интерфейс LPC 225

Рис. 6.15. Протокол LPC

В поле START возможны следующие коды:

¦ 0000 — начало цикла обращения хоста к устройству;

¦ 0010 — предоставление доступа ведущему устройству 0;

¦ ООН — предоставление доступа ведущему устройству 1;

¦ 1111 — принудительное завершение цикла (abort).

Остальные коды зарезервированы.

Поле CYCTYPE задает тип и направление передачи. Бит 0 задает направление (0 — чтение, 1 — запись), биты [2:1] — тип обращения (00 — порт, 01 — память, 10 — DMA, 11 — резерв), бит 3 — резерв (0).

Поле TAR (Turn-Around) служит для смены «владельца» шины LAD[3:0], оно занимает 2 такта. В первом такте прежний владелец помещает код 1111, во втором переводит буферы в третье состояние.

Поле ADDR служит для передачи адреса. В цикле памяти оно занимает 8 тактов (32 бита), в цикле ввода-вывода — 4 такта. Передача адреса начинается со старших битов (чтобы раньше срабатывал дешифратор адреса).

В поле DATA передаются данные. На каждый байт требуется 2 такта, передача начинается с младшей тетрады. Многобайтные передачи начинаются с младшего байта. Поле SYNC служит для введения тактов ожидания устройством, к которому выполняется обращение. Оно может содержать следующие коды (остальные зарезервированы):

¦ 0000 — готовность (без ошибок), для DMA означает снятие запроса для данного канала;

¦ 0101 — короткое ожидание (несколько тактов);

¦ 0110 —длинное ожидание;

¦ 1001 — готовность и присутствие запроса для канала DMA (для других типов

обращения недопустимо);

¦ 1010 — ошибка: данные переданы, но возникли условия, при которых на ши

нах PCI или ISA выработался бы сигнал SERR* или ЮСНК# (для DMA также

означает снятие сигнала запроса).

226_____________________________________ Глава 6. Шины и карты расширения

Поле синхронизации обеспечивает контроль передачи, введение тактов ожидания и механизм тайм-аутов.

Начав цикл, хост читает поле синхронизации. Если в течение трех тактов адресованное устройство не ответит, хост считает, что его нет на шине, и прекращает транзакцию. Если приходит код короткого ожидания, хост дожидается его смены на готовность или ошибку, но после 8 тактов ожидания он прервет транзакцию по тайм-ауту. Код длинного ожидания может приходить сколь угодно долго, ответственность за отсутствие зависания ложится на адресованное устройство. При прямом управлении поле SYNC выставляется хостом, и устройство должно терпеливо ожидать готовности, без каких-либо тайм-аутов. В самом быстром варианте (без тактов ожидания) поле SYNC занимает один такт.

На рис. 6.16 приведена последовательность полей при обращениях хоста к памяти или портам (серым цветом помечены поля, вводимые устройством). Во всех этих обращениях передается по одному байту. Для чтения памяти, предполагая 5 тактов поля SYNC (время доступа к EPROM 120 не), требуется 21 такт (0,63 мкс), что обеспечивает скорость чтения памяти 1,59 Мбайт/с. Если память конвейеризирована, то последующие обращения будут быстрее. Для записи в память поле SYNC займет 1 такт, а весь цикл — 17 тактов (0,51 мкс), что дает скорость записи 1,96 Мбайт/с. Обращения к портам за счет более короткой адресации и без тактов ожидания (1 такт SYNC) занимают по 13 тактов (0,39 мкс), что дает скорость 2,56 Мбайт/с для чтения и записи.

|

а | START |

CYCTYPE |

ADDR |

TAR |

lsyNc |

DATA |

TAR |

|

б | START |

CYCTYPE |

ADDR |

DATA |

TAR |

SYNQ |

TAR |

Для организации обмена по DMA и прямого управления хост должен иметь по одной входной линии LDRQ* для каждого подключенного устройства, использующего эти функции. По этой линии устройство передает состояние запросов каналов DMA в последовательном коде, как показано на рис. 6.17. Посылка начинается со старт-бита, за которой следуют код номера канала и бит запроса ACT: 1 (высокий уровень) — запрос активен, 0 — пассивен.

Номер канала 4 ( код 100) зарезервирован для прямого управления (он соответствует традиционно недоступному каналу DMA). Посылка передается при каждой смене состояния запросов. Нормально таким способом передается лишь запрос, а снятие его сигнализируется полем SYNC. Передама, данных DMA (рис. 6.18) выполняется под управлением хоста, но несколько отличается от обычных обращений к портам и памяти. Здесь появляются новые поля:

¦ поле SIZE определяет размер передачи: 0000 — 1 байт, 0001 — 2 байта, 0011 —4 байта, остальные значения зарезервированы;

¦ поле CHANNEL служит для передачи хостом номера канала DMA (биты [2;0])

и признака конца цикла (ТС, бит 3).

6.4. Интерфейс LPC

227

Рис. 6.17. Посылка запроса DMA или прямого управления

|

А |

START |

CYCTYPE |

CHANNEL |

SIZE |

DATA |

TAR |

,ЈSYNC |

TAR | |

|

б |

START |

CYCTYPE |

CHANNEL |

SIZE |

TAR |

SYNC |

DATA |

TAR |

Циклы чтения памяти, в зависимости от длины обращения (1, 2 или 4 байта), без тактов ожидания (они скрыты контроллером DMA) занимают 11,18 и 32 тактов (0,33, 0,54 или 0,96 икс), что обеспечивает производительность 3,03, 3,70 или 4,17 Мбайт/с соответственно. Циклы записи занимают 11,14 или 20 тактов (0,33, 0,42 или 0,60 мкс), что обеспечивает производительность 3,03,4,76 или 6,67 Мбайт/с. На рисунке выделены рамкой последовательности полей, повторяющиеся при передаче 2 и 4 байтов.

Прямое управление шиной ведущее устройство запрашивает так же, как и прямой доступ, но указывая зарезервированный номер канала 4 (100). Предоставляя управление, хост в поле START задает номер мастера, который позже определит тип цикла (рис. 6.19). Прямое управление подразумевает обращение к ресурсам хоста (системной памяти, устройству PCI). Данные в 2- и 4-байтных передачах следуют друг за другом без зазора, но в циклах чтения памяти и портов всегда будут такты ожидания, поскольку потребуется время на арбитраж шины PCI или доступ к контроллеру памяти.

Из расчета 6 тактов (меньше — вряд ли, возможно и больше) поля SYNC, циклы обращения к памяти (и чтения, и записи) потребуют 25,27 или 31 такт (0,75, 0,81 или 0,93 мкс), что обеспечивает производительность 1,33, 2,47 или 4,30 Мбайт/с. За счет более короткой адресации обращение к портам быстрее — 21, 23 или 27 тактов (0,63, 0,69 или 0,81 мкс), что обеспечивает производительность 1,59, 2,90 или 4,94 Мбайт/с.

|

а | START |

TAR |

CYCTYPE |

ADDR |

SIZE |

TAR |

SYNC |

DATA |

TAR |

|

б | START |

TAR |

CYCTYPE |

ADDR |

SIZE . |

DATA |

TAR |

SYNC |

TAR |

б — запись в память (порт)

Электрический интерфейс для сигналов LAD[3:0], LFRAME#, LDRQ# и SERIRQ соответствует спецификации PCI 2.1 для питания 3,3 В. Остальные сигналы в зависимости от системной платы могут быть с уровнями как 5 В, так и 3,3 В.

228____________________________________ Глава 6. Шины и карты расширения

Конфигурирование устройств LPC не предусматривает использования протоколов PCI или ISA PnP, поскольку все устройства LPC априорно известны системной BIOS. Для обращения к устройствам LPC хост должен декодировать их адреса и направлять обращения по ним на контроллер LPC.

Интерфейс MIDI

Цифровой интерфейс музыкальных инструментов MIDI (Musical Instrument Digital Interface) является последовательным асинхронным интерфейсом с частотой передачи 31,25 Кбит/с. Этот интерфейс, разработанный в 1983 году, стал фактическим стандартом для сопряжения компьютеров, синтезаторов, записывающих и воспроизводящих устройств, микшеров, устройств специальных эффектов и другой электромузыкальной техники. В настоящее время интерфейс MIDI имеют и дорогие синтезаторы, и дешевые музыкальные клавиатуры, которые могут использоваться в качестве устройств ввода компьютера. По интерфейсу MIDI устройства обмениваются между собой сообщениями, кратко описанными в книге [1]. На одном интерфейсе может быть организовано до 16 логических каналов, каждый из которых может управлять своим инструментом.

В физическом интерфейсе применяется токовая петля 5мА (возможно до 10 мА) с гальванической (оптронной) развязкой входной цепи. Логическому нулю соответствует наличие тока, логической единице (и покою) — отсутствие тока (в «классической» токовой петле телекоммуникаций все наоборот).

346

Глава 8. Специализированные интерфейсы периферийных устройств

Интерфейс определяет три типа портов: MIDI-In, MIDI-Out и MIDI-Thru. Входной порт MIDI-In представляет собой вход интерфейса «токовая петля», гальванически развязанного от приемника оптроном с быстродействием не хуже 2 мкс. Устройство отслеживает информационный поток на этом входе и реагирует на адресованные ему команды и данные.

Выходной порт MIDI-Out представляет собой выход источника тока, гальванически связанного со схемой устройства. Ограничительные резисторы предохраняют выходные цепи от повреждения при замыкании на землю или источник 5 В. На выход подается информационный поток от данного устройства. При специальной настройке устройства в этом потоке может содержаться и транслированный входной поток, но это нетипично.

Транзитный порт MIDI-Thru служит только для ретрансляции входного потока, по электрическим свойствам он аналогичен выходному.

Его наличие не является обязательным для всех устройств.

В качестве разъемов применяются 5-контактные разъемы DIN, распространенные в бытовой звуковой аппаратуре, схема соединительного кабеля приведена на рис. 8.17.

Рис. 8.17. Соединительные кабели MIDI

Внешний порт MIDI (с сигналами ТТЛ) обычно выводится на неиспользуемые контакты (12 и 15) разъема игрового адаптера (DB-15S). При этом для подключения стандартных устройств MIDI требуется переходной адаптер, реализующий интерфейс «токовая петля» (на разъеме карты интерфейс ТТЛ). Переходной адаптер обычно встраивается в специальный кабель, вариант схемы которого приведен на рис. 8.18. Некоторые модели PC имеют встроенные адаптеры и стандартные 5-штырьковые разъемы MIDI.

Программно порт MIDI обычно совместим с UART MPU-401. MPU-401 фирмы Roland — первая карта расширения для PC с интерфейсом MIDI, получившая широкое распространение. MPU расшифровывается как MIDI Processing Unit — устройство обработки сообщений MIDI. Этот контроллер кроме асинхронного последовательного порта (UART), реализующего физический интерфейс MIDI, имел развитые аппаратные средства для использования PC в качестве секвенсора. Контроллер MPU-401 поддерживал простой режим работы — UART mode, в котором использовался только двунаправленный асинхронный порт; в современных звуковых картах совместимость с MPU-401 поддерживается только в этом режиме.

8.5. Интерфейсы аудиоустройств

347

Рис. 8.18. Вариант схемы кабеля-адаптера MIDI

В пространстве ввода-вывода MPU-401 занимает два смежных адреса MPU (обычно ЗЗОЬ)и MPU+1.

¦ Порт DATA (адрес MPU+0) — запись и считывание байт, передаваемых и принимаемых по интерфейсу MIDI. В интеллектуальном режиме через этот же порт считываются и вспомогательные данные от MPU (не относящиеся к потоку MIDI).

¦ Порт STATUS/COMMAND (адрес MPU+1) — чтение состояния/запись команд (запись — только для интеллектуального режима).

В байте состояния определены следующие биты:

• бит 7 — D5R (Data Set Ready) — готовность (DSR=0) принятых данных для чтения (бит устанавливается в единицу, когда все принятые байты считаны из регистра данных);

• бит 6 — DRR (Data Read Ready) — готовность (DRR=0) UART к записи в регистр данных или команд (условие готовности к записи не возникнет, если

приемник имеет непрочитанный байт данных).

По включении питания «настоящая» карта MPU-401 устанавливается в интеллектуальный режим, из которого в режим UART ее можно перевести командой с кодом 3Fh. Программный сброс MPU-401 (опять-таки в интеллектуальный режим) осуществляется командой RESET (код FFh), на эту команду MPU ответит подтверждением АСК (FEh). Байт подтверждения извлекается из регистра данных, до его прихода следующую команду MPU не воспримет. На команду с кодом 3Fh MPU подтверждением не отвечает (некоторые эмуляторы отвечают и на эту команду).

Ввод данных может осуществляться по программному опросу бита DSR или по прерываниям. Аппаратные прерывания от MPU в режиме UART вырабатываются по приему байта. Обработчик прерывания должен считать все поступившие байты, проверив перед выходом, что DSR-1 (иначе возможны потери принятых байт).

348________ Глава 8. Специализированные интерфейсы периферийных устройств

Вывод данных разрешается битом DRR, прерывания по готовности вывода не вырабатываются.

Совместимость с MPU-401, имеющаяся у большинства современных звуковых карт с интерфейсом MIDI, означает наличие приемопередатчика, программно совместимого с MPU-401 в режиме UART; функции интеллектуального режима обычно не поддерживаются.

На некоторых системных платах применяются БИС контроллеров интерфейсов, в которых режим UART, используемый для СОМ-порта, конфигурированием через BIOS SETUP может быть переведен в режим MIDI-порта.

Для подключения к компьютеру большого числа устройств MIDI можно использовать шину USB.Для этого, например, фирма Roland выпускает 64-канальный процессорный блок S-MPU64, который кроме шины USB имеет 4 входных и 4 выходных порта MIDI. Программное обеспечение допускает объединение до 4 блоков на одной шине USB, что увеличивает число каналов до 256.

Интерфейс НГМД

Накопители на гибких магнитных дисках (НГМД) подключаются к контроллеру через специальный стандартный интерфейс. Основные функции по управлению НГМД, а также кодирование-декодирование данных выполняет контроллер, расположенный на большинстве современных системных плат. Раньше контроллер часто выносили на специальную карту расширения («в компании» с интерфейсом НЖМД). На плате электроники, установленной на корпусе НГМД, расположены только схемы приводов двигателей, усилители-формирователи сигналов записи и считывания и формирователи сигналов от датчиков.

Интерфейс RS-

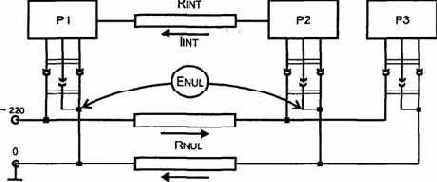

Интерфейс RS-232C предназначен для подключения аппаратуры, передающей или принимающей данные ( 00Д — оконечное оборудование данных, или АПД — аппаратура передачи данных; DTE — Data Terminal Equipment), к оконечной аппаратуре каналов данных {АКД; DCE—Data Communication Equipment). В роли АПД может выступать компьютер, принтер, плоттер и другое периферийное оборудование. В роли АКД обычно выступает модем. Конечной целью подключения является соединение двух устройств АПД. Полная схема соединения приведена на рис. 2.1; интерфейс позволяет исключить канал удаленной связи вместе с парой устройств АКД, соединив устройства непосредственно с помощью нуль-модемного кабеля (рис. 2.2).

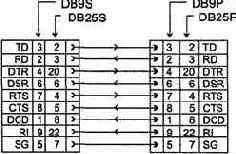

Рис. 2.2. Соединение по RS-232C нуль-модемным кабелем

50________________________ Глава 2. Последовательный интерфейс —> СОМ-порт;

Стандарт описывает управляющие сигналы интерфейса, пересылку данных, электрический интерфейс и типы разъемов. В стандарте предусмотрены асинхронный и синхронный режимы обмена, но СОМ-порты поддерживают только асинхрон-ныйрежим. Функционально RS-232Cэквивалентен стандарту МККТТ V.24/ V.28 и стыку С2, но они имеют различные названия сигналов.

Стандарт RS-232C описывает несимметричные передатчики и приемники — сигнал передается относительно общего провода — схемной земли (симметричные дифференциальные сигналы используются в других интерфейсах — например, RS-422). Интерфейс не обеспечивает гальванической развязки устройств. Логической единице соответствует напряжение на входе приемника в диапазоне от -12 до -3 В. Для линий управляющих сигналов это состояние называется ON («включено»), для линий последовательных данных — MARK. Логическому нулю соответствует диапазон от +3 до +12 В. Для линий управляющих сигналов состояние называется OFF («выключено»), а для линий последовательных данных — SPACE. Диапазон от -3 до +3 В — зона нечувствительности, обусловливающая гистерезис приемника: состояние линии будет считаться измененным только после пересечения порога (рис. 2.3).

Уровни сигналов на выходах передатчиков должны быть в диапазонах от -12 до -5 В и от +5 до +12 В для представления единицы и нуля соответственно. Разность потенциалов между схемными землями (SG) соединяемых устройств должна быть менее 2 В, при более высокой разности потенциалов возможно неверное восприятие сигналов.

Интерфейс предполагает наличие защитного заземления для соединяемых устройств, если они оба питаются от сети переменного тока и имеют сетевые фильтры.

ВНИМАНИЕ---------------------------------------------------------------------------------

Подключение и отключение интерфейсных кабелей устройств с автономным питанием должно производиться при отключенном питании. Иначе разность невыровненных потенциалов устройств в момент коммутации может оказаться приложенной к выходным или входным (что опаснее) цепям интерфейса и вывести из строя микросхемы.

На аппаратуре АПД (в том числе на СОМ-портах) принято устанавливать вилки ПВ-25Р или более компактный вариант — DB-9P. Девятиштырьковые разъемы не имеют контактов для дополнительных сигналов, необходимых для синхронного режима (в большинстве 25-штырьковых разъемах эти контакты не используются).

На аппаратуре АКД (модемах) устанавливают розетки DB-25S или DB-9S.

Это правило предполагает, что разъемы АКД могут подключаться к разъемам АПД непосредственно или через переходные «прямые» кабели с розеткой и вилкой, у которых контакты соединены «один в один». Переходные кабели могут являться и переходниками с 9 на 25-штырьковые разъемы (рис. 2.4).

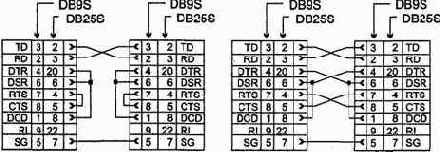

Если аппаратура АПД соединяется без модемов, то разъемы устройств (вилки) соединяются между собой нуль-модемным кабелем (Zero-modem, или Z-modem), имеющим на обоих концах розетки, контакты которых соединяются перекрестно по одной из схем, приведенных на рис. 2.5.

2.1. Интерфейс RS-232C

51

|

|

|

Рис. 2.5. Нуль-модемный кабель: а — минимальный, б — полный

52

Глава 2. Последовательный интерфейс — СОМ-порт

В табл. 2.1 приведено назначение контактов разъемов СОМ-портов (и любой другой аппаратуры передачи данных АПД). Контакты разъема DB-25S определены стандартом EIA/TIA-232-E, разъем DB-9S описан стандартом EIA/TIA-574. У модемов (АКД) название цепей и контактов такое же, но роли сигналов (вход-выход) меняются на противоположные.

Таблица 2.1. Разъемы и сигналы интерфейса RS-232C

|

Обозначение цепи |

Контакт |

№ провода кабеля |

Направление |

||||||

|

разъема |

выносного разъема PC |

||||||||

|

СОМ- |

RS- |

V.24 |

DB- |

DB- |

11 |

2х |

З3 |

Л* |

I/O |

|

порт |

232 |

Стык 2 |

25Р |

9Р |

|||||

|

PG |

АА |

101 |

1 |

5 |

(10) |

(10) |

(10) |

1 |

- |

|

SG |

АВ |

102 |

7 |

5 |

5 |

9 |

1 |

13 |

- |

|

TD |

ВА |

103 |

2 |

3 |

3 |

5 |

3 |

3 |

О |

|

RD |

ВВ |

104 |

3 |

2 |

2 |

3 |

4 |

5 |

I |

|

RTS |

СА |

105 . |

4 |

7 |

7 |

4 |

8 |

7 |

О |

|

CTS |

СВ |

106 |

5 |

8 |

8 |

6 |

7 |

9 |

I |

|

DSR |

СС |

107 |

6 |

6 |

6 |

2 |

9 |

11 |

I |

|

DTR |

CD |

108/2 |

20 |

4 |

4 |

7 |

2 |

14 |

О |

|

DCD |

CF |

109 |

8 |

1 |

1 |

1 |

5 |

15 |

I |

|

RI |

СЕ |

125 |

22 |

9 |

9 |

8 |

6 |

18 |

I |

2 Ленточный кабель 16-битных мультикарт и портов на системных платах.

3 Вариант ленточного кабеля портов на системных платах.

4 Широкий ленточный кабель к 25-контактному разъему.

Подмножество сигналов RS-232C, относящихся к асинхронному режиму, рассмотрим с точки зрения СОМ-порта PC. Для удобства будем пользоваться мнемоникой названий, принятой в описаниях СОМ-портов и большинства устройств (она отличается от безликих обозначений RS-232 и V.24).

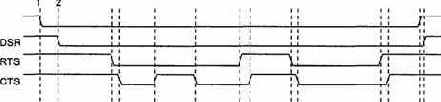

Напомним, что активному состоянию сигнала («включено») и логической единице передаваемых данных соответствует отрицательный потенциал (ниже -3 В) сигнала интерфейса, а состоянию «выключено» и логическому нулю — положительный (выше +3 В). Назначение сигналов интерфейса приведено в табл. 2.2. Нормальную последовательность управляющих сигналов для случая подключения модема к СОМ-порту иллюстрирует рис. 2.6.

2.1. Интерфейс RS-232C

53

Таблица 2.2. Назначение сигналов интерфейса RS-232C

SG Signal Ground — сигнальная (схемная) земля, относительно которой действуют уровни сигналов

TD Transmit Data — последовательные данные — выход передатчика

RD Receive Data — последовательные данные — вход приемника

RTS Request To Send — выход запроса передачи данных: состояние «включено»

уведомляет модем о наличии у терминала данных для передачи. В полудуплексном режиме используется для управления направлением — состояние «включено» служит сигналом модему на переключение в режим передачи

CIS Clear To Send — вход разрешения терминалу передавать данные. Состояние

«выключено» запрещает передачу данных. Сигнал используется для аппаратного управления потоками данных

DSR Data Set Ready — вход сигнала готовности от аппаратуры передачи данных (модем в рабочем режиме подключен к каналу и закончил действия по согласованию с аппаратурой на противоположном конце канала)

DTR Data Terminal Ready — выход сигнала готовности терминала к обмену данными.

Состояние «включено» поддерживает коммутируемый канал в состоянии соединения

DCD Data Carrier Detected — вход сигнала обнаружения несущей удаленного модема

Rl Ring Indicator — вход индикатора вызова (звонка). В коммутируемом канале этим

сигналом модем сигнализирует о принятии вызова

|

3 4 |

7 8 |

9 1 |

11 12 1314 |

DTR |

1. Установкой DTR компьютер указывает на желание использовать модем.

2. Установкой DSR модем сигнализирует о своей готовности и установлении соединения.

3. Сигналом RTS компьютер запрашивает разрешение на передачу и заявляет о своей готовности принимать данные от модема.

4. Сигналом CTS модем уведомляет о своей готовности к приему данных от компьютера и передаче их в линию.

5. Снятием CTS модем сигнализирует о невозможности дальнейшего приема (например, буфер заполнен) — компьютер должен приостановить передачу данных.

6. Сигналом CTS модем разрешает компьютеру продолжить передачу (в буфере появилось место).

54________________________ Глава 2. Последовательный интерфейс — СОМ-нюрт

7. Снятие RTS может означать как заполнение буфера компьютера (модем должен приостановить передачу данных в компьютер), так и отсутствие данных для передачи в модем. Обычно в этом случае модем прекращает пересылку данных в компьютер.

8. Модем подтверждает снятие RTS сбросом CTS.

9. Компьютер повторно устанавливает RTS для возобновления передачи.

10. Модем подтверждает готовность к этим действиям.

11. Компьютер указывает на завершение обмена.

12. Модем отвечает подтверждением.

13. Компьютер снимает DTR, что обычно является сигналом на разрыв соединения («повесить трубку»).

14. Модем сбросом DSR сигнализирует о разрыве соединения.

Из рассмотрения этой последовательности становятся понятными соединения DTR-DSR и RTS-CTS в нуль-модемных кабелях.

Интерфейс SPI

Интерфейс SPI (Serial Peripheral Interface), он же Microwire, — трехпроводный синхронный с раздельными линиями входных и выходных данных — применяется для связи микроконтроллеров с периферийными микросхемами и микросхемами памяти. С его помощью программируются многие микросхемы программируемой логики (например, FPGA фирмы Altera), применяемые в различных узлах ПК и периферии. По сравнению с 12С интерфейс SPI обеспечивает более высокую скорость передачи данных. Частота синхронизации может достигать 5 МГц (зависит от подключаемых устройств); при этом за каждый такт синхронизации одновременно может и передаваться, и приниматься очередной бит данных. В основном варианте использования предполагается, что интерфейс соединяет одно ведущее устройство с одним или несколькими ведомыми устройствами. Интерфейс может применяться и для обмена между несколькими микроконтроллерами, допуская наличие на шине нескольких ведущих устройств, но протокол предоставления доступа не стандартизован. Ниже рассматривается работа интерфейса с одним ведущим устройством. В интерфейсе используются 3 обязательных сигнала:

¦ SCK (Serial Clock) — синхросигнал, которым ведущее устройство стробирует каждый бит данных;

¦ MOSI (Master Output Slave Input) — выходные данные ведущего устройства и входные данные ведомого устройства;

¦ MISO (Master Input Slave Output) — входные данные ведущего устройства и выходные данные ведомого устройства.

11.3. Интерфейс SPI

445

При этом получа ется гибридная топология соединений: по сигналам SCK, MOSI и MISO — топология шинная, по SS# — звездообразная (центр — ведущее устройство).

Возможен и иной способ общения ведущего устройства с несколькими ведомыми устройствами с чисто шинной топологией. Здесь сигнал SS# для выбора устройств не используется, но ведомые устройства все время «слушают» шину, ожидая специальной адресной посылки в начале транзакции. Опознав свой адрес, устройство отрабатывает дальнейшие протокольные посылки, и теперь ему разрешается выводить данные на линию MISO до конца текущей транзакции. Однако этот вариант требует довольно сложной логики поведения ведомого устройства.

Рис. 11.5. Форматы передач по интерфейсу SPI

Данные передаются старшим битом вперед. Устройства различных производителей могут использовать разные режимы обмена (SPI Mode 0... SPI Mode 3), различающиеся фазой и полярностью синхросигналов. Рис. 11.5 иллюстрирует передачу и прием байта в различных режимах. Заметим, что в любом режиме входные и выходные данные стробируются по разным перепадам синхроимпульсов. Кроме того, есть варианты в использовании сигнала SS#. В первом варианте (он и представлен на рисунке) для ведомого устройства признаком начала транзакции является спад сигнала SS#, а завершения — его подъем. Во втором варианте начало транзакции определяется по первому фронту (спаду) SCK, а сигнал SS# может иметь низкий уровень постоянно. Второй вариант иногда предпочитают для простейшего двухточечного интерфейса с единственным ведущим устройством и единствен-

446__________ Глава 11. Вспомогательные последовательные интерфейсы и шины

ным ведомым устройством, когда нет опасения потери синхронизации. Микроконтроллеры с аппаратным портом SPI, как правило, имеют возможность программного выбора режима. Форматы транзакций зависят от устройств, но общая идея такова: ведущее устройство по линии MOSI посылает код операции и адресную информацию для устройства; затем следуют данные.В операции записи они передаются ведущим устройством по той же линии, в операции чтения устройство их посылает по линии MISO. На время всей транзакции ведущее устройство сохраняет активное состояние линии SS#, число требуемых синхроимпульсов зависит от формата команды.

Интерфейсы аудиоустройств

Звуковая карта имеет набор разъемов для подключения внешних аудиосигналов, аналоговых и цифровых, а также интерфейс MIDI для связи с электронными музыкальными инструментами. Аудиоданные в цифровом виде могут передаваться также и по универсальным шинам USB и Fire Wire (см. п. 4.2).

Интерфейсы блока питания PC

Блок питания PC обеспечивает напряжениями постоянного тока системный блок со всеми его сложными и часто «привередливыми» устройствами. С самых первых моделей PC здесь применяется двухтактная схема преобразователя с бестрансформаторным входом; без революционных изменений эта схема дошла и до наших дней. Преобразователь является регулирующим элементом стабилизатора напря-

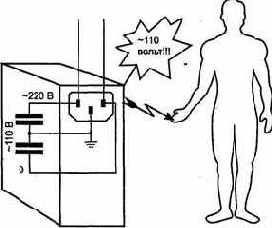

512_______ Глава 13. Интерфейсы питания, заземление и гальваническая развязка

жения основного источника +5 В. Остальные напряжения могут быть стабилизированы дополнительными выходными стабилизаторами, но чаще их оставляют нестабилизированными. При этом чем больше нагрузка блока по основной (стабилизированной) цепи, тем выше напряжения на остальных шинах. Блоки питания PC не критичны к частоте сети (50 или 60 Гц) и могут работать даже от сети постоянного тока. Относительно старые блоки питания имеют переключатели диапазона входного напряжения. Переключение диапазона входного напряжения легко осуществляется переключателем, который преобразует мостовую схему выпрямителя в схему выпрямителя с удвоением для питания от сети 110-127 В. При включении блока, предназначенного для работы при напряжении ПО В, в сеть 220 В часто выходят из строя ключевые транзисторы или диоды. Современные блоки, у которых указано свойство Autoswitching Power Supply, имеют компоненты с большим запасом по допустимому напряжению и не требуют переключения номинала входного питающего напряжения — они работают в диапазоне 110-230 В.

Блок питания PC обычно имеет стандартный конструктив и набор жгутов с разъемами питания системной платы и периферийных устройств. Выключатель питания в старых конструктивах располагался на боковой или задней стенке блока питания. Позже его вынесли с блока питания на лицевую панель корпуса и стали присоединять к блоку кабелем со съемными контактами. К этому кабелю, проходящему через весь системный блок, следует относиться с вниманием, поскольку он является источником опасности и помех.

В конструктиве АТХ главный вы ключатель питания вернулся на блок питания, а с передней панели блоком питания управляют с помощью кнопки.

Мощность блока питания зависит от назначения корпуса системного блока и лежит в диапазоне от 100-150 Вт для обычных компьютеров и до 350-500 Вт для мощных серверов.

Традиционный (не АТХ) блок питания вырабатывает основное стабилизированное напряжение +5 В при токе до 10-50 А; +12 В при токе 3,5-15 А для питания двигателей устройств и интерфейсных цепей; -12 В при токе 0,3-1 А для питания интерфейсных цепей; -5 В при токе 0,3-0,5 А (обычно не используется, присутствует только для соблюдения стандарта ISA Bus).

Кроме питающих напряжений блок вырабатывает сигнал P.G. (Power Good) — питание в норме. Этот сигнал с уровнем в 3-6 В вырабатывается через 0,1-0,5 с после включения питания при нормальных выходных напряжениях блока. При отсутствии этого сигнала на системной плате непрерывно вырабатывается сигнал аппаратного сброса процессора, появление сигнала «выпускает» систему в нормальную работу. Этот сигнал должен сброситься раньше, чем пропадет напряжение +5 В при отключении блока. Отсутствие должной задержки сигнала при включении и запаздывание при выключении может приводить к потере информации в CMOS и ошибкам при загрузке по включении питания. Нажатие кнопки Reset по действию почти эквивалентно замыканию сигнала P.G. на «схемную землю».

13.3. Интерфейсы блока питания PC

513

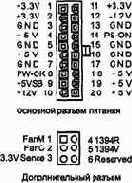

Выходные цепи блоков питания выводятся гибкими жгутами проводов со стандартным набором разъемов (рис. 13.7). Разъемы для питания накопителей имеют ключи, исключающие возможность неправильного соединения. Однако иногда встречаются блоки с ошибочно собранными разъемами, в результате на шину питания +5 В попадает +12 В, чего устройства, как правило, не выдерживают. Такая ошибка в практике автора привела, например, к выходу из строя подряд двух 3" дисководов — ошибку в питании стали искать лишь после обнаружения неработоспособности второго дисковода.

Традиционные разъемы питания системной платы PS-8, PS-9 всегда устанавливаются рядом так, чтобы четыре черных провода GND шли подряд. Их ключи весьма условны, а ошибка подключения чревата выгоранием системной платы. Цвета проводов в жгутах стандартизованы:

¦ GND — черный;

¦ -12V —коричневый;

¦ +5V — красный;

¦ -5V — голубой;

¦ + 12V —желтый;

¦ P.G. — белый (питание в норме).

Рис. 13.7. Выходные разъемы традиционного блока питания

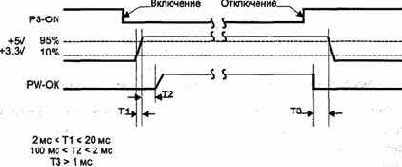

Блок питания в стандарте А7Х значительно отличается от традиционных блоков питания как по габаритным размерам, так и по электрическому интерфейсу. Блок имеет дополнительный источник напряжением +3,3 В для питания процессора и «дежурный» (Standby) маломощный источник с выходной цепью +5VSB. Дежурный источник с допустимым током нагрузки 10 мА (АТХ 2.01) включается при подаче сетевого напряжения. Он предназначен для питания цепей управления энергопотреблением и устройств, активных и в спящем режиме (например, факсмодема, способного при поступлении входящего звонка «разбудить» машину). В дальнейшем предполагается увеличить мощность данного источника до допустимого тока 720 мА, что позволит «будить» компьютер даже по приему пакета от дежурного адаптера локальной сети. В интерфейс блока питания введен управляющий сигнал PS-ON, включающий основные источники +5, +3,3, +12, -12 и -5 В (рис. 13.8). Напряжение от этих источников поступает на выход блока только при

514

Глава 13. Интерфейсы питания, заземление и гальваническая развязка

удержании сигнала PS-ON на низком логическом уровне. При высоком уровне или свободном состоянии цепи выходные напряжения этих источников поддерживаются около нулевого уровня. О нормальном напряжении питания сигнализирует сигнал PW-OK (Power O'Key), по действию аналогичный сигналу P.G. традиционных блоков. Интерфейс управления питанием позволяет выполнять программное отключение питания.

Рис. 13.8. Временная диаграмма интерфейса управления питанием АТХ

Все питающие и сигнальные провода к системной плате подключаются одним основным разъемом с надежным ключом (рис. 13.9, а). На разъемах подключения накопителей, естественно, сохранилось традиционное назначение контактов.

Расширенная спецификация для блока питания АТХ предусматривает передачу информации от датчиков вентилятора на системную плату, что обеспечивает контроль скорости вращения вентилятора и температуры воздуха. Для этих целей предназначен дополнительный (необязательный) жгут с разъемом, изображённый на рис. 13.9, б. Сигнал FanM представляет собой выход типа «открытый коллектор» от тахометрического датчика вентилятора блока питания, вырабатывающего два импульса на каждый оборот ротора. Сигнал FanC предназначен для управления скоростью вентилятора подачей напряжения в диапазоне 0...+12 В при токе до 20 мА. Если уровень напряжения выше +10,5 В, вентилятор будет работать на максимальной скорости. Уровень ниже +1 В означает запрос от системной платы на остановку вентилятора. Промежуточные значения уровня позволяют плавно регулировать скорость. Внутри блока питания сигнал FanC подтягивается к уровню +12 В, так что, если дополнительный разъем оставить неподключенным, вентилятор будет всегда работать на максимальной скорости. На дополнительном разъеме также имеются контакты 1394V (+) и 1394R (-) изолированного от схемной земли источника напряжения 8-48 В для питания устройств шины IEEE-1394 (FireWire). Цепь +3.3V Sense служит для подачи сигнала обратной связи стабилизатору напряжения +3,3 В.

13.3. Интерфейсы блока питания PC 515

Рис. 13.9. Разъемы блока питания АТХ для подключения к системной плате

Цепи блоков питания АТХ имеют стандартизованную цветовую маркировку:

¦ СОМ - черный (соответствует цепи GND традиционных блоков);

¦ +5V — красный;

¦ +12V—желтый;

¦ -5V - белый;

¦ -12V— синий;

¦ +3.3V — оранжевый;

¦ +3.3V Sense — коричневый (может подходить к контакту 11);

¦ +5VSB — малиновый;

¦ PS-ON — зеленый;

¦ PW-ON-серый.

Дополнительный разъем:

¦ +3.3V Sense — белый с коричневыми полосками;

¦ FanC — белый с синими полосками;

¦ FanM — белый;

¦ 1394V — белый с красными полосками;

¦ 1394R —белый с черными полосками.

Интерфейсы графических адаптеров

Для подключения дисплея (монитора) к графическому адаптеру компьютера используются специализированные/интерфейсы, по которым передается информация о мгновенном значении яркости базисных цветов (RGB) и сигналы строчной и кадровой синхронизации. Способ передачи уже прошел первый виток спирали развития: от дискретного интерфейса первых адаптеров (MDA, CGA, EGA) через аналоговый интерфейс VGA снова возвращаются к цифровому способу (DVI, P&D, DFP). Интерфейсы мониторов в большинстве своем стандартизованы организацией VESA (www.vesa.org).

Видеоинтерфейсы используются для вывода информации на обычные телеприемники и телевизионные мониторы, а также ввода видеоданных в компьютер. Видеоданные в цифровом виде могут передаваться и приниматься по шине Fire Wire, а также по USB версии 2.0.

Многие графические адаптеры имеют внутренний разъем VFC или VAFC — это параллельная шина для обмена пиксельной информацией с дополнительными картами видеообработки.

К системе (процессору и памяти) графический адаптер подключается через какую-либо шину расширения (AGP, PCI, ISA), их интерфейсы описаны в главе 6.

Интерфейсы и конструктивы твердотельных носителей информации

Твердотельные устройства хранения используются в миниатюрных компьютерах, а также компьютеризированных цифровых устройствах бытовой электроники — фотокамерах, плейерах, приемниках глобальной системы позиционирования (GPS), музыкальных инструментах и прочих. В большинстве своем эти устройства основаны на микросхемах флэш-памяти, в наиболее современных используется память со структурой NAND (см. п. 7.3.2). Этому типу флэш-памяти присуще быстрое чтение, запись и стирание небольших блоков (256 или 512 байт), что удобно для записи файлов. Правда, для этой памяти характерны довольно медленное чтение произвольного байта и отсутствие возможности побайтной записи, но приложениям этих карт такая возможность и не требуется, поскольку они ориентированы на блочный обмен. Устройства на флэш-памяти являются энергонезависимыми (в режиме хранения не требуют питания), экономичными в плане потребления,

9.3. Интерфейсы и конструктивы твердотельных носителей информации

395

Есть и другие твердотельные хранители — например, ферроэлектрическая память (FRAM), но пока что массового применения они не имеют. Менее чем за десятилетие устройства хранения на флэш-памяти прошли большой путь от электронных «дисков» («винчестеров») размером в 3" до современных, размером с почтовую марку.

Интерфейсы твердотельных устройств хранения — карт внешней памяти — тесно связаны с их конструктивами; основные характеристики наиболее распространенных карт приведены в табл. 9.12.

Таблица 9.12. Основные характеристики карт внешней памяти

|

CompactFlash |

SmartMedia |

MultiMedia |

Sequre |

Miniature |

|

|

Card |

Card |

Digital |

Card |

||

|

Длина |

36,0 |

45,0 |

32,0 |

32,0 |

33,0 |

|

Ширина |

43,0 |

37,0 |

24,0 |

24,0 |

38,0 |

|

Высота |

3,3/5,0 |

0,76 |

1,4 |

2,1 |

3,5 |

|

Коннектор |

Штырьковый |

Печатный |

Печатный |

Печатный |

Эластомер |

|

Число контактов |

50 |

22 |

7 |

9 |

60 |

В качестве интерфейса твердотельных устройств хранения может использоваться и самый обычный вариант AT А. Существуют устройства DOM (Disk On Module) — небольшие модули, которые вставляются в обычный 40-контактный разъем АТА, имеющийся на любой современной системной плате. Правда, этот «винчестер» не блещет выдающимися параметрами: объем — 4-256 Мбайт, средняя скорость передачи данных — 1,6 Мбайт/с, удельная стоимость хранения — около $1,5 за мегабайт. Внутри модуля находится флэш-память структуры NAND с контроллером, эмулирующим систему команд АТА. Основное применение этих модулей — хранение ПО встраиваемых компьютеров, но можно ими пользоваться и как сменными устройствами хранения.

396

Глава 9. Интерфейсы устройств хранения

Интерфейсы мыши

Мышь является устройством, предназначенным для ввода координат и подачи команд. Интерфейс мыши применим для любого физического воплощения устройства (мышь, трекбол). По интерфейсу с компьютером различают три основных вида мышей: Bus Mouse, Serial Mouse и PS/2-Mouse. Появились мыши с интерфейсом USB, но они пока не получили широкого распространения (как и клавиатура USB, к порту которой удобно подключить мышь USB).

8.2. Интерфейсы мыши__________________________________________ 317

С интерфейсами Serial Mouse и PS/2-Mouse иногда возникают недоразумения. Хотя оба они последовательные, но имеют существенные принципиальные различия в уровнях сигналов, способе синхронизации, частоте и формате посылок.

¦ Интерфейс PS/2 использует однополярный сигнал с уровнями ТТЛ, питание мыши — однополярное с напряжением +5 В относительно шины GND. Интерфейс RS-232C, применяемый в Serial Mouse, использует двуполярный сигнал (см. п. 2.1) с уровнями срабатывания +3 В и -3 В, и для него требуется двупо-лярное (относительно шины GND) питание мыши.

¦ Интерфейс PS/2 использует две раздельные сигнальные линии, одну для пе

редачи данных, другую — для сигналов синхронизации. Serial Mouse использует асинхронный способ передачи данных всего по одной линии.

Даже не рассматривая частоты и форматы посылок, становится ясно, что прямой совместимости между этими интерфейсами быть не может. Тем не менее выпускаются и продаются переходники (пассивные!), позволяющие выбирать способ подключения мыши. Эти переходники предназначены только для универсальных мышей, у которых встроенный контроллер по напряжению питания способен распознать, к какому интерфейсу его подключили, и установить соответствующий тип своего выходного интерфейса. Универсальные мыши не особо распространены, поэтому часто приходится слышать о неудачных попытках применения таких переходников к обычной мыши Serial Mouse или PS/2-Mouse.

Дополнительную путаницу вносят мыши для компьютера Macintosh, которые имеют разъем, с виду напоминающий разъем PS/2. Однако при ближайшем рассмотрении и неудачной попытке включения его в PC становится ясно, что разъемы эти разные, да и интерфейс совершенно иной.

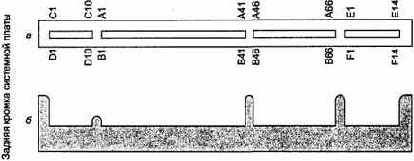

Интерфейсы PCMCIA, PC Card и CardBus

В начале 90-х годов организация PCMCIA (Personal Computer Memory Card International Association — международная ассоциация производителей карт памяти для персональных компьютеров) начала работы по стандартизации шин расширения блокнотных компьютеров, в первую очередь предназначенных для расширения памяти. Первым появился стандарт PCMCIA Standard Release 1.0/JEIDA 4.0 (июнь 1990 г.), в котором был описан 68-контактный интерфейс и два типоразмера карт: Туре I и Туре II PC Card. Поначалу стандарт касался электрических и физических требований только для карт памяти. Был введен метаформат информационной структуры карты CIS (Card Information Structure), в которой описываются характеристики и возможности карты, — ключевой элемент взаимозаменяемости карт и обеспечения механизма PnP.

6.5. Шины и карты расширения блокнотных ПК__________________________ 229

Следующая версия PCMCIA 2.0 (1991 г.) для того же разъема определила интерфейс операций ввода-вывода, двойное питание для карт памяти, а также методики тестирования. В версии 2.01 была добавлена спецификация PC CardATA, новый типоразмер Туре III, спецификация автоиндексируемой массовой памяти AIMS (Auto-Indexing Mass Storage) и начальный вариант сервисной спецификации (Card Services Specification). В версии 2.1 (1994 г.) расширили спецификации сервисов карт и сокетов (Card and Socket Services Specificaiton) и развили структуру CIS.

Стандарт PC Card (1995 г.) явился продолжением предыдущих; в нем введены дополнительные требования для улучшения совместимости и новые возможности: питание 3,3 В, поддержка DMA и 32-битного режима прямого управления шиной CardBus. В дальнейшем в стандарт были введены и другие дополнительные возможности.

Все карты PCMCIA и PC Card имеют 68-контактный разъем, назначение контактов у которого варьируется в зависимости от типа интерфейса карты. Тип интерфейса «заказывается» картой при установке ее в слот, который, естественно, должен поддерживать требуемый интерфейс. Интерфейс памяти обеспечивает 8- и 16-битные обращения с минимальным временем цикла 100 не, что дает максимальную производительность 10 и 20 Мбайт/с соответственно. Интерфейс ввода-вывода имеет минимальную длительность цикла 255 не, что соответствует 3,92/7,84 Мбайт/с для 8-/16-битных обращений. Интерфейс CardBus поддерживает практически такой же протокол обмена, что и PCI, но с некоторыми упрощениями.

Тактовая частота 33 МГц и разрядность 32 бита обеспечивают пиковую пропускную способность в пакетном цикле до 132 Мбайт/с, картам предоставляется возможность прямого управления шиной (bus mastering). Здесь используется та же система автоматического конфигурирования, что и в PCI (через регистры конфигурационного пространства). В интерфейс заложены дополнительные возможности для цифровой передачи аудиосигнала, причем как в традиционной форме ИКМ, так и в новой (забытой старой) форме ШИМ (PWM).

Для дисковых устройств АТА в формате PC Card имеется специальная спецификация интерфейса (см. п. 9.2.1).

Различают 4 типа PC Card: у них у всех размер в плане 54 х 85,5 мм, но разная толщина (меньшие адаптеры встают в большие гнезда):

¦ PC Card Type I — 3,3 мм — карты памяти;

¦ PC Card Type II — 5 мм — карты устройств ввода-вывода, модемы, адаптеры локальных сетей;

¦ PC Card Type III — 10,5 мм — дисковые устройства хранения;

¦ PC Card Type IV — 16 мм (упоминания об этом типе на сайте www.pc-card.com найти не удалось).

Есть еще и маленькие карты Small PC Card размером 45 х 42,8 мм с тем же коннектором и теми же типами по толщине.

Для карт памяти (динамической, статической, постоянной и флэш-памяти) ассоциация PCMCIA поддерживает и стандарт Miniature Card (см. п. 9.3.4).

230

Глава 6. Шины и карты расширения

Назначение контактов разъемов для разных типов интерфейса приведено в табл. 6.18, назначение сигналов для интерфейсов карт памяти и ввода-вывода — в табл. 6.19. Для карт CardBus обозначение сигналов начинается с префикса «С», за которым следует имя сигнала, принятое для шины PCI (см. п. 6.2.2).

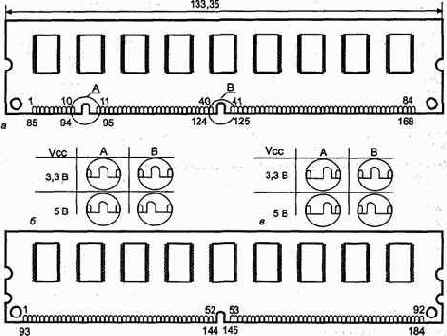

Таблица 6.18. Разъем PC Card

|

№ |

Тип интерфейса |

№ |

Тип интерфейса |

||||

|

16 бит |

32 бита |

16 бит |

32 бита |

||||

|

Mem |

l/O+Mem |

CardBus |

Mem |

l/O+Mem |

CardBus |

||

|

1 |

GND |

GND |

GND |

35 |

GND |

GND |

GND |

|

2 |

D3 |

D3 |

CADO |

36 |

CD1# |

CD1# |

CCD1# |

|

3 |

D4 |

D4 |

CAD1 |

37 |

D11 |

D11 |

CAD2 |

|

4 |

D5 |

D5 |

CAD3 |

38 |

D12 |

D12 |

CAD4 |

|

5 |

D6 |

D6 |

CAD5 |

39 |

D13 |

D13 |

CAD6 |

|

6 |

D7 |

D7 |

CAD7 |

40 |

D14 |

D14 |

Резерв |

|

7 |

СЕ1# |

CE1# |

CCBEO* |

41 |

D15 |

D15 |

CAD8 |

|

8 |

А10 |

A10 |

CAD9 |

42 |

CE2# |

CE2# |

CAD10 |

|

9 |

ОЕ# |

OE# |

CAD11 |

43 |

VS1# |

VS1# |

CVS1 |

|

10 |

А11 |

A11 |

CAD12 |

44 |

Резерв |

IORD# |

CAD13 |

|

11 |

А9 |

A9 |

CAD14 |

45 |

Резерв |

IOWR# |

CAD15 |

|

12 |

А8 |

A8 |

CCBE1* |

46 |

A17 |

A17 |

CAD 16 |

|

13 |

А13 |

A13 |

CPAR |

47 |

A18 |

A18 |

Резерв |

|

14 |

А14 |

A14 |

CPERR# |

48 |

A19 |

A19 |

CBLOCK# |

|

15 |

WE# |

WE# |

CGNT# |

49 |

A20 |

A20 |

CSTOPff |

|

16 |

READY |

IREQ# |

CINT# |

50 |

A21 |

A21 |

CDEVSEL* |

|

17 |

Vcc |

Vcc |

VCC |

51 |

Vcc |

Vcc |

Vcc |

|

18 |

Vpp1 |

Vpp1 |

Vpp1 |

52 |

VPP2 |

Vpp2 |

Vpp2 |

|

19 |

A16 |

A16 |

CCLK |

53 |

A22 |

A22 |

CTRDY» |

|

20 |

A15 |

A15 |

CIRDY* |

54 |

A23 |

A23 |

CFRAME# |

|

21 |

A12 |

A12 |

CCBE2# |

55 |

A24 |

A24 |

CAD17 |

|

22 |

A7 |

A7 |

CAD 18 |

56 |

A25 . |

A25 |

CAD 19 |

|

23 |

A6 |

A6 |

CAD20 |

57 |

VS2# |

VS2# |

CVS2 |

|

24 |

A5 |

A5 |

CAD21 |

58 |

RESET |

RESET |

CRST# |

|

25 |

A4 |

A4 |

CAD22 |

59 |

WAIT# |

WAIT# |

CSERR# |

|

26 |

A3 |

A3 |

CAD23 |

60 |

Резерв |

INPACK* |

CREQ# |

|

27 |

A2 |

A2 |

CAD24 |

6t |

REG# |

REG# |

CCBE3* |

|

28 |

A1 |

A1 |

CAD25 |

62 |

BVD2 |

SPKR# |

CAUDIO |

|

29 |

АО |

АО |

CAD26 |

63 |

BVD1 |

STSCHG* |

CSTSCHG |

|

30 |

DO |

DO |

CAD27 |

64 |

D8 |

D8 |

CAD28 |

|

31 |

D1 |

D1 |

CAD29 |

65 |

D9 |

D9 |

CAD30 |

|

32 |

D2 |

D2 |

Резерв |

66 |

D10 |

D10 |

CAD31 |

|

33 |

WP |

IOIS16» |

CCLKRUN* |

67 |

CD2# |

CD2# |

CCD2# |

|

34 |

GND |

GND |

GND |

68 |

GND |

GND |

GND |

6.5. Шины и карты расширения блокнотных ПК

231

I/O

Назначение

|

А[10:0] |

I |

|

BVD1.BVD2 |

I/O |

|

STSCHGff |

I/O |

|

SPKR# |

0 |

|

CD1#,CD2# |

0 |

|

СЕ1#,СЕ2# |

I |

|

D[15:0] INPACK# |

I/O 0 |

|

IORD# IOWR# |

1 1 |

|

OE# RDY/BSY# IREQ# INTRQ REG# |

1 1 0 0 1 |

|

RESET VS1#,VS2# |

1 о |

|

WAIT» WE# |

0 1 |

|

WP |

0 |

|

IOCS16# |

0 |

Battery Volt Detection — идентификаторы батарейного питания

(Ю) Сигнализация хосту о смене состояния RDY/BSY* и Write Protect. Использование этого сигнала контролируется регистром управления и состояния карты Card Config and Status Register

(Ю) Дискретный аудиовыход (на динамик)

Card Detect — сигналы обнаружения (заземлены на карте), по которым хост определяет, что карта полностью вставлена в слот

(Ю, Mem) Card Enable — выбор (разрешение) карты и определение разрядности передачи. Сигнал СЕ2# всегда относится к нечетному байту, СЕ1 # — к четному или нечетному, в зависимости от АО и СЕ2#. С помощью этих сигналов 8-битный хост может обмениваться с 16-битными картами по линиям D[7:0]

Шина данных (у 8-битных сигналы D[15:8] отсутствуют)

(Ю) Input Acknowledge — подтверждение ввода, ответ карты на сигнал IORD* (по этому сигналу хост открывает свои буферы данных)

Строб команды чтения портов

Строб команды записи портов (данные должны фиксироваться по положительному перепаду)

Чтение данных из памяти, конфигурационных регистров и CIS Готовность карты к обмену данными (при высоком уровне) Запрос прерывания (низким уровнем) Запрос прерывания (высоким уровнем)

Выбор памяти атрибутов (Mem). Для карт Ю сигнал должен быть активен в циклах команд ввода-вывода. В режиме IDE пассивен (соединен с Vcc на стороне хоста)

Сброс (высоким уровнем)

Voltage Sense — сигналы определения номинала питания. Заземленный сигнал VS1 # означает способность чтения карты при питании 3,3 В

Запрос (низким уровнем) на продление цикла обращения

Строб записи в память и конфигурационные регистры ( в IDE не используется, соединяется хостом с Vcc)

Write Protect — защита от записи (для карт памяти), запись в память возможна при низком уровне

Разрешение 16-битного обмена

232 ____________________________________ Глава 6. Шины и карты расширения

сигнал REG#, действующий одновременно с СЕ# и адресом. Для обращения к портам ввода-вывода служат отдельные сигналы IORD* и IOWR#; во время их действия должен быть активен и сигнал REG#. В процессе обращения к портам карта может выдать признак возможности 16-битных обращений сигналом IOSC16* (как на шине ISA). Чтение порта устройство должно подтверждать сигналом INPACK*, устанавливаемым и снимаемым картой по сигналу СЕ#. Благодаря этому сигналу хост может убедиться в том, что он читает не пустой слот.

Слоты PC Card могут предоставлять возможность прямого доступа к памяти (DMA). Реализация DMA — самый дешевый способ разгрузки процессора, но такая реализация имеется не на всех хостах, а только на простых, основанных на шине ISA. Для систем с шиной PCI более естественно прямое управление шиной CardBus, правда, для карт реализация прямого управления обходится не дешево.

Для мультимедийных карт имеется возможность переключения интерфейса в специальный режим ZVPort (Zoomed Video), в котором организуется отдельный двухточечный интерфейс передачи данных между картой и хост-системой. По смыслу интерфейс напоминает коннектор VFC графических карт — выделенная шина для передачи видеоданных, не связанная с остальными шинами (и не загружающая их), но имеет иной протокол.

В режиме ZV Port адресные линии А[25:4], а также линии BVD2/SPKR*, INPACK* и IOIS16# получают иное назначение — по ним передаются видеоданные и 4 цифровых аудиоканала. Для обычного интерфейса остаются лишь 4 адресные линии, позволяющие адресоваться к 16 байтам общей памяти и атрибутов карты.

Интерфейс порта ZV соответствует временным диаграммам CCIR601, что позволяет декодеру NTSC в реальном времени доставлять видеоданные с карты в экранный буфер VGA. Видеоданные могут поступать на карту как с внешнего видеовхода, так и с декодера MPEG.

Карты имеют специальное выделенное пространство памяти атрибутов, в котором находятся конфигурационные и управляющие регистры карты, предназначенные для автоконфигурирования. Стандартом описан формат информационной структуры карты (Card Information Structure, CIS). Карты могут быть многофункциональными (например, комбинация модема и сетевого адаптера). В спецификации MFPC (Multiple Function PC Cards) для каждой функции предусматриваются отдельные конфигурационные регистры и определяются правила разделения (совместного использования) линии запроса прерывания.

Для устройств внешней памяти стандарт описывает форматы хранения данных, совместимые с FAT MS-DOS, а также ориентированные на флэш-память как основной носитель информации. Для непосредственного исполнения модулей ПО, хранящихся в ПЗУ карты, имеется спецификация XIP (eXecute In Place), описывающая программный интерфейс вызова этих модулей (вместо загрузки ПО в ОЗУ).

Стандарт описывает программный интерфейс сервисов карт (Card Services), обеспечивающий унификацию взаимодействия его клиентов (драйверов, прикладно-

6.5. Шины и карты расширения блокнотных ПК __________________ 233

го ПО и утилит) с устройствами. Имеется также и интерфейс сервисов сокета (Socket Services), с помощью которого выполняются операции, связанные с обнаружением фактов подключения-отключения карт, их идентификации, конфигурирования питания и аппаратного интерфейса.

В стандарте имеются описания специфических особенностей, свойственных двум организациям, ведущим стандарт PC Card.

¦ PCMCIA описывает автоиндексируемую массовую память (AIMS) для хранения больших массивов данных (изображений, мультимедийных данных) на блочно-ориентированных устройствах. Имеется также спецификация 15-контактного экранированного разъема для подключения модемов и адаптеров локальной сети (15-pin Shielded Modem I/O connector) и 7-контактного для подключения модемов (7-pin Modem I/O connector).

¦ JEDIA для карт памяти предлагает формат файлов Small Block Flash Format, упрощающий файловую систему. Формат SISRIF (Still Image, Sound and Related Information Format) предназначен для записи изображений и звука на карты памяти. Имеется и спецификация для карт динамической памяти.

Большинство адаптеров выпускается с поддержкой технологии PnP и предусматривает «горячее» подключение — интерфейсные карты могут вставляться и выниматься без выключения компьютера. Для этого контакты шин питания имеют большую длину, чем сигнальные, обеспечивая их упреждающее подключение и запаздывающее отключение. Два контакта обнаружения карты CD1 # и CD2# (Card Detect) короче остальных — их замыкание для хоста означает, что карта полностью вставлена в слот. Несмотря на возможность динамического конфигурирования, в некоторых случаях при изменении конфигурации требуется перезагрузка системы.

Первоначально карты и хост-системы использовали напряжение питания логики +5 В. Для перехода на низковольтное питание (3,3 В) был введен механический ключ, не допускающий установки карты на 3,3 В в слот, дающий только 5 В. Кроме того, были определены контакты 43 (VS1#) и 57 (VS2#) для выбора питающего напряжения. На картах с питанием 5 В они оба свободны; на картах 3,3 В контакт VS1# заземлен, a VS2# свободен. По этим линиям хост, допускающий оба варианта напряжения питания, определяет потребности установленной карты и подает соответствующее напряжение.

Если хост не способен обеспечить требуемый номинал, он должен не подавать питание, а выдать сообщение об ошибке подключения. Карты обычно поддерживают управление энергопотреблением (АРМ), что особо актуально при автономном питании компьютера.

В стандарте PC Card выпускают самые разнообразные устройства — память, устройства хранения, коммуникационные средства, интерфейсные порты, игровые адаптеры, мультимедийные устройства и т. п., правда, все они существенно дороже своих крупногабаритных аналогов. Через слот PC Card портативные компьютеры могут подключаться к док-станциям, в которые может быть установлена обычная