Адресация устройств PCI

Для шины PCI принята иерархия понятий адресации: шина, устройство, функция. Эти понятия фигурируют только при обращении к регистрам конфигурационного пространства (см. п. 6.2.12). К этим регистрам обращаются на этапе конфигурирования — переучета обнаруженных устройств, выделения им непересекающихся ресурсов (областей памяти и пространства ввода-вывода) и назначения номеров аппаратных прерываний. При дальнейшей регулярной работе устройства будут отзываться на обращения по назначенным им адресам памяти и ввода-вывода, доведенным до сведения связанных с ними модулей ПО. Эти адреса принимаются с шины AD в начале каждой транзакции. Для доступа к конфигурационному пространству используются отдельные линии IDSEL

Устройством PCI называется микросхема или карта расширения, подключенная к одной из шин PCI и использующая для идентификации выделенную ей линию IDSEL, принадлежащую этой шине. Устройство может быть многофункциональным, то есть состоять из множества (от 1 до 8) так называемых функций. Каждой функции отводится конфигурационное пространство в 256 байт (см. п. 6.2.12). Многофункциональные устройства должны отзываться только на конфигурационные циклы с номерами функций, для которых имеется конфигурационное пространство. При этом функция с номером 0 должна быть обязательно, номера остальных функций назначаются разработчиком устройства произвольно (в диапазоне 1-7). Простые (однофункциональные) устройства, в зависимости от реализации, могут отзываться либо на любой номер функции, либо только на номер функции 0.

Шина PCI — набор сигнальных линий (см. п. 6.2.2), непосредственно соединяющих интерфейсные выводы группы устройств (слотов, микросхем на системной плате). В системе может присутствовать несколько шин PCI, соединенных мостами PCI (см. п. 6,2.10). Мосты электрически отделяют интерфейсные сигналы одной шины от другой, соединяя их логически; главный мост соединяет главную шину с ядром системы (процессором и памятью). Каждая шина имеет свой номер шины (PCI bus number).

Шины нумеруются последовательно; главная шина имеет нулевой номер.

С точки зрения конфигурирования, минимальной адресуемой единицей этой иерархии является функция; ее полный адрес состоит из трех частей: номера шины, номера устройства и номера функции. Короткая форма идентификации вида РСЮ:1:2 (например, в сообщениях ОС Unix) означает функцию 2 устройства 1, подключенного к главной (0) шине PCI.

6.2. Шина PCI______________________________________________________ 177

В шине PCI принята географическая адресация — номер устройства определяется местом его подключения. Номер устройства (device number или dev) определяется той линией шины AD, к которой подключена линия сигнала IDSEL данного слота: kADU -devO(MOCT),AD12-devl,...AD31 -dev20. В соседних слотах PCI, как правило, задействуются соседние номера устройств; их нумерация определяется разработчиком системной платы (или пассивной кросс-платы в промышленных компьютерах). Часто для слотов используются убывающие номера устройств, начиная с 20. Группы соседних слотов могут подключаться к разным шинам; на каждой шине PCI нумерация устройств независимая (могут быть и устройства с совпадающими номерами dev, но разными номерами шин). Устройства PCI, интегрированные в системную плату, используют ту же систему адресации. Их номера «запаяны намертво», в то время как адреса карт расширения можно изменять перестановкой их в разные слоты. Одна карта PCI может содержать только одно устройство шины, к которой она подключается, поскольку ей в слоте выделяется только одна линия IDSEL Если на карте размещают несколько устройств (например, 4-портовая карта Ethernet), то на ней приходится устанавливать мост — тоже устройство PCI, к которому и обращаются по линии IDSEL, выделенной данной карте. Этот мост организует на карте дополнительную шину PCI, к которой можно подключить множество устройств.

С точки зрения обращения к пространствам памяти и ввода-вывода, географический адрес (номер шины и устройства) безразличен (не принимая во внимание разницу в производительности, связанную с подключением устройств к разным шинам PCI).

Однако номер устройства определяет номер линии запроса прерывания, которой может пользоваться устройство. Подробнее об этом см. в п. 6.2.6, здесь же отметим, что на одной шине устройства с номерами, отличающимися друг от друга на 4, будут использовать одну и ту же линию прерывания. Возможность развести их по разным линиям прерывания может появиться лишь, если они находятся на разных шинах (это зависит от системной платы).

Разобраться с нумерацией устройств и полученных ими линий прерываний на конкретной плате можно просто: устанавливать одну карту PCI поочередно в каждый из слотов (отключая питание) и смотреть на сообщения об обнаруженных устройствах PCI, выводимых на дисплей в конце теста POST. В этих сообщениях будут фигурировать и устройства PCI, установленные непосредственно на системной плате (и не отключенные параметрами CMOS Setup).

Но чтобы не было иллюзий простоты и прозрачности, отметим, что «особо умные» операционные системы (Windows) не довольствуются полученными назначениями номеров прерывании и изменяют их по своему усмотрению (что никак не может отразиться на разделяемости линий).

Алфавитный указатель

lOOOBaseCX, 406

lOOOBaseLX, 406

lOOOBaseSX, 406

lOOOBaseT, 406

100BaseFX, 406

lOOBaseSX, 406

100BaseT4, 406

100BaseTX, 406

10Base2, 406

lOBaseS, 405

lOBaseF, 406

lOBaseT, 406

168-pin Registered DIMM, 267

168-pin Unbuffered DIMM, 267

A20, 313,315 ACCESS.Bus, 331,427 Additional ROM BIOS, 497 AGP, 211 режим Ix, 218 2x, 218 4x, 218 сигналы, 212 слот, 219 транзакции, 213 AGP Pro, 221 AGP8X, 223 APIC, 461 ASK IR, 79 ATA, 359

Bus-Master, 383 PIO Mode, 377 Ultra DMA, 377 адаптер, 382 джамперы, 388 кабельная выборка, 387 каналы, 383

конфигурирование устройств, 387 протокол, 380 регистры устройства, 371 режим передачи, 376 DMA, 377 PIO, 376 сигналы, 363,366

ATA (продолжение)

устройства Master и Slave, 360

, хост-адаптер, 360 ,

электрический интерфейс, 362

АТА-2, 361

АТА-3, 361

ATA/ATAPI-4, 361,362

ATAPI, 360

ATX, разъем питания, 513

AUI, 409

В

BEDO 240

Bi-tron'ics, 20

BIOS

32-разрядные вызовы, 480, /

СОМ-порт, 69,491,493

IntOSh, 325

Int 08h, 358

Int09h, 316,325

IntOEh, 357

Int 13h, 403

Int l4h, 48

Int 15h, 478

Int16h, 316

Int17h, 17,320,325

Int 19h, 498

Int 1 Ah, 210,478

Int 33h, 318

PCI, 210

SMBus, 440

видеорежимы, 486

интерфейс клавиатуры, 484

клавиатура, 316

мышь, 318

принтер, 325

расширение, 497

сервисы, 481

стандартные драйверы дисков, 487 BIOS Int 15h, 495 BIOS Int 16h, 484,493 BIOS Int 1Ah, 494 BIOS Int 9h, 483 BIOS32, 480 Bluetooth, 82 ВМС-разъемы, 332

518

Алфавитный указатель

Bootable CD-ROM, 404 Boundary Scan, 447 bus mastering, 411,465 Bus-Master, 360,383 Byte Mode, 24

DRAM, 235 BEDO, 240 EDO, 239

DTE, 49

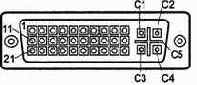

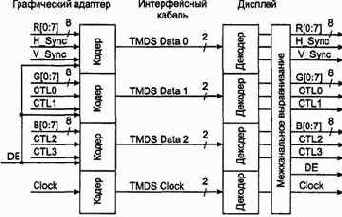

DVI, 337

Caller Id, 418 CardBus, 229 CAS Latency, 241 CD-ROM

загружаемый, 404

системная поддержка, 404 Centronics, 321 CHS, адресация, 360 CMOS

RTC, 477

память конфигурации и часы, 477

программирование таймера, 478,495

таймер, 477 СОМ-порт, 70

UART 8250/16450/16550, 63

использование, 70

конфигурирование, 70

неисправности и тестирование, 73

питание от интерфейса, 76

поддержка BIOS, 69,493

разъемы, 52 Compact PCI, 196 Composite Video, 341 cPCI 196 CR, 321

ОСЕ, 49

DDC1, 331

DDC2, 331

DDC2AB, 331

DDC2B, 331

DDIM, 499

DDMA, 465

DDR SDRAM, 267

DFP, 336

dial-up, 414

DIMM, 261

DiskOnChip, 479

DMA, 21,70,157,463 '

16-битные каналы, 465

8-битные каналы, 464

LPT-порт, 21

PC/PCI, 465

каналы, 464

пересечение границ, 473 DPMS, 332

E-IDE, 362 ECP, 22,29,322 EDD, 490 EDO, 239 EEPROM, 164 EISA, 146,151,164 El Tonto, 404 EOI, 459 EPP, 22,25 Ethernet, 405 AUI, 409 7^j£ 410 адаптер, 412 AUI/ 413 BNC, 413 Combo, 413 ТР, 413

интерфейсы, 413 конфигурирование, 414 ресурсы, 413 серверный, 412 интерфейсная карта, 410 коммутатор, 405 перекрестный кабель, 407 повторитель, 405 прямой кабель, 407 сетевой адаптер, 410 согласование режимов, 409 EVC, 333 expansion bus, 145 Expansion ROM, 497,503 Extended ASCII Keystroke, 485

fast ATA-2, 361

Fast Centronics, 21

Fast Ethernet, 406

Fast IP) 412

Fast SCSI, 117

Fast Wide SCSI, 117

FCAL 140

FDC, 356

Feature connector, 340

Fibre Channel, 140 адаптер, 141 коммутатор, 141 концентратор, 141 маршрутизатор, 141 мост, 141

Алфавитный указатель

519

адаптер, 112

асинхронные сообщения, 110

динамическое реконфигурирование, 111

диспетчер изохронных ресурсов, 111

изохронные передачи, 110

использование, 113

кабельная сеть, 107

контроллер шины, 112

мастер циклов, 111

протокол, 109

разъем, 107

сравнение с USB, 87

устройства, 112 Flow Control, 60 FOIRL, 406 FRAM, 305

Game-порт, 349 GateA20, 315,469 Gigabit Ethernet, 406

H

Handshaking, 60 HPЧТП7SllMAf, »U

I

PC, 331,421 i8042, 313 IDE

ATA, AT-BUS, 361

XT, 371

разновидности интерфейса, 361 IEEE 1149.1, 446 IEEE 1284, 22,322

ECP, 29

EPP, 25

LPT-порт, 22

PnP, 41

двунаправленный обмен, 24

кабели и разъемы, 40

полубайтный обмен, 23 IEEE 1394, 106,109 IN, 376

Infra Red Connection, 78 Int05h, 325 IntO8h, 358 Int09h, 316,325 IntOEh, 357,487 Int 10h, 71 Int13h, 142,403

Int I3h (продолжение)

параметры вызова, 487

функции 00-24h, 487 41-49h, 491 4A-4D, 491 Int u^ 4g59,71, 491 Int 15h' 478 Int 16h, 71,316 Int17h, 17,320,325 Int 19h, 498 Int lAh, 210,478 Int33h, 318 Int 40h, 486 Int 76h, 487 Int 9h, 484 Ir TP, 80 IR-Connector, 81 IrCOMM, 80 IrDA, 78

FIR, 79

HDLC, 79

MIR, 79

SIR, 79

приемопередатчики, 81 IrDA4PPM, 80 IrLAN, 81 IrLAP, 80 IrLMP, 80 IrOBEX, 81 IRQ 15, 487 IRQ 6, 487 IRQ11, 70 IRQ4, 70 IRQ5> 20 IRQ7, 20 ISA, 146

bus mastering, 159

Bus-Master, 360

legacy card, 165

PnP, 165

каналы DMA, 147

карта

безджамперная, 164 прототип, 146

конфигурирование, 164

порты PnP, 165

прерывания, 147,160

пространство памяти, 147

прямое управление шиной 159

прямой доступ к памяти, 157

распределение ресурсов, 147

регенерация памяти, 159

сигналы, 149

слот, 148

шина, 146 ISO_8482, 56

520

Алфавитный указатель

JTAG, 446 jumperless, 164,414

OFF-Line, 321 OUT, 376 Output Enable, 156

LapLink, 18 LBA, адресация, 361 Legacy Card, 455 LF, 321 Loop Back, 46 Low-Profile PCI, 196 LPC, 223 LPT-порт, 17

Fast Centronics, 21

IEEE 1284, 22

двунаправленный, 21

использование, 42

кабель подключения принтера, 323

конфигурирование, 44

расширения, 21

с прямым доступом к памяти, 21

связь компьютеров, 42

стандартный определение, 18 прерывания, 20 регистры, 19

тестирование, 45

функции BIOS, 41

м

Magic Packet, 412

Master, 360

MDI, 407

MDIX, 407

Ml-PC, 232

Microwire, 444

MIDI, 345,350

Mil, 410

Miniature Card, 229,402

, 400

mouse

Bus, 319

MS Mouse, 317

PC Mouse, 317

PS/2, 318

Serial, 317 MPU-401, 346 MultiMediaCard, 400

N

Nibble Mode, 20,23 NIC, 410 NVRAM, 277

P&D, 336 P&D-A, 333 P&D-A/D, 336 PC Card, 229

сигналы, 229

шина, 228 PC/104, 161 PC/PCI, 465 PC/PCI DMA, 191 PCI, 175

BIOS, 210

concurrency, 199

posted write, 200

автоконфигурирование, 204

адресация, 183

арбитраж, 179

ведомое устройство, 177

завершение транзакции, 181

классы устройств, 209

команды, 185

конфигурационный механизм, 202

мост, 198

номер

устройства, 177 шины, 176

отложенные транзакции, 199

позитивное декодирование, 198

прерывания, 189

сигналы, 177

слоты, 192193

субтрактивное декодирование, 198

таймеры/ 182

устройство, 176

частота шины, 193

шина, 175

электрический интерфейс, 192

эмуляция DMA, 191 PCI Bridge, 198 PCI IDE> 384 PCI-X, 196 PCMCIA, 228 Peer-to-Peer Bridge, 198 PIO, 376,473 PIO Mode, 377 PnP BIOS, 500 PS/2, 21 pulse dialing, 416 PXI, 197

Алфавитный указатель

RCА, разъемы, 341 RDRAM, 245,269

инициализация, 249

канал, 246

пакеты, 247 refresh, 238 RGB Analog, 327 RJ-11, 415 RAM, 22,30 ROM BIOS, 454,500 RS-232C, 49,55,389

аппаратное управление потоком RTS/CTS, 61

микросхемы UART, 63

программное управление

потоком XON/XOFF, 62 RS-422, 55,56,57 RS-423 55 RS-485, '55,56,57

S-VHS, 342 S-Video, 341 S/PDIF, 344 SBA, 213 SCAM, 116 SCSI SPI, 115

адресация устройств, 129 версии, 116

дифференциальная версия, 116 инициатор обмена, 129 кабели, 118,120 конфигурирование, 134,142 линейная версия, 116 низковольтный дифференциальный

интерфейс LVD, 117 подключение устройств, 135 разъем

СХ-50, 119

DB-25, 119

HD-50, 119

HD-68, 119

IDC-50, 118

MiniDSO, 119

MiniD68, 119

SCA, 120

VHDCI-68, 120 разъемы, 118,121 система команд, 143 терминаторы, 125 узкий интерфейс, 116

SCSI (продолжение)

управление, 142

фазы 129

хост-адаптер, 141

целевоеустройство, 129

шина, 114,134,142 SCSI.2>

ш SCSI-3, 115 SD 4(ю

SDRAM, 240,245,262 Secure Digital, 400 Self-Healing Driver, 412 Serial ATA, 389 Setup, 44 SIMM, 257 SIMM-30, 257 SIPP, 256 Slave, 360

SmartMedia Card, 399 SMBus, 433 SMI Mil, 443 SPCI, 196 SPI, 115,444 SPP, 18 SRAM, 274

Tagged VLAN, 412 TinyTP, 80 tone dialing, 416 Toslink, 345 lype l, 21

и

UART, 63

8250/16450/16550, СОМ-порт, 63 MPU-401, 346 RS-232C, 63

Ultra DMA, 361,362,377

Ultra SCSI, 117

Ultral60SCSI, 117

Ultra2SCSI, 117

Ultra320 SCSI, 117

unreal, 471

USB, 88

автоконфигурирование, 101 адаптивные устройства, 99 асинхронные устройства, 98 взаимодействие, 89 высокая скорость (HS), 88 изохронные передачи, 97 интерфейс, 90 кадры, 95

522

Алфавитный указатель

USB (продолжение) канал, 95

конечные точки, 94 микрокадр, 96 низкая скорость (LS), 88 передачи массивов данных, 96 подключение устройств, 91 полная скорость (FS), 88 поток, 95

преобразователи интерфейсов, 103 прерывания, 97 применение 101 протокол, 95 синхронизация, 97 синхронные устройства, 98 сообщения, 95 сравнение с FireWire, 87 удаленное пробуждение, 94 управление энергопотреблением, 93 управляющие посылки, 96 устройства, 88 функции, 89 хаб, 92 хост, 89,99 хост-контроллер, 100 шина> 88

V.11, 56

VESA, 332

VESA DDC, 331

VESA Feature connector, 340

VGA Palette Snooping, 201

VP&D, 336

VT-100, 71

VT-42 71

w

Wide Ultra SCSI, 117 Wide Ultra2 SCSI, 117

X27 56 XON/XOFF 62

Y

Y/C, 342

z

ZV Port, 232

автоконфигурирование

PCI, 204

USg 1Q1

устройств, 204 адаптер

АТА, 382

bus master, 411

Ethernet, 410

Fibre Channel, 141

ЛВС, подключение, 43 адресация

CHS, 360

LBA, 361

ввода-вывода, 223

канальная, 30

памяти, 216,223 адресный пакет, 491 АКД, 49

аналоговые аудиоинтерфейсы, 342 АОН, 417 АПД, 49

аппарат телефонный, 415 асинхронный режим, 50

байтный ввод, 24 барьер

528 Мбайт, 489 блок питания

АТХ, 513

PC, 511

сетевой фильтр, 505

традиционный, 512 блокированный телефон, 417

В

ввод

байтный, 24

двунаправленный, 24

полубайтный, 23 ввод-вывод

РЮ, 473

дешифрация 10/12 бит, 455

инструкции, 473

карта

разрешенных обращений, 474 распределения портов, 456 вентиль линии А20, 315 видео

графические режимы, 486 видеоинтерфейсы, 341 видеосигнал, 341 виртуальная память, 470 ВЛС, 412 выборка кабельная, 387

Алфавитный указатель

52<$

д

двунаправленный LPT-порт, 21 двунаправленный ввод, 24 двунаправленный обмен, 24 джойстик, 349 дискеты

дисковый сервис, 486 диски АТА

логические параметры, 490 физические параметры, 490 дисковый сервис BIOS, 486 расширенный, 490 традиционный, 487 дисплейный адаптер BNC-разъемы, 332 VESA Feature Connector, 339 VGA Auxiliary Video Connector, 339 идентификация монитора, 331 интерфейс DDC, 331 RGBTTL, 326 RGB аналоговый, 327 композитный видеосигнал, 341 управление энергопотреблением

монитора, 332

дифференциальный интерфейс SCSI, 116 драйвер самоизлечивающийся, 412 дуплексный обмен, 14

заземление, 506 зануление, 507 защищенный режим, 469 звуковая карта, 348

И

идентификация

источника запроса прерывания, 161

монитора, 331

питания, 402 интерфейс

ACCESS.bus, 442

AUI, 409

DDC, дисплейный адаптер, 331

DFP, 336

DVI, 337

интерфейс (продолжение) Ethernet, 405 PC, 421,442 IrDA, 78 JTAG, 446 LPC, 223 microwire, 444 МП, 410 P&D, 336

RGBTTL, дисплейный адаптер, 326 RGB аналоговый, 327 RS-232C, 55 RS-422, 55 RS-423, 55 RS-485, 55 S-VHS, 342 S-video, 341 S/PDIF, 344 . SCSI, 116 Serial ATA, 389 SMBus, 442 SMI, 443 SPI, 444 USB, 90 Y/C, 342 аудио, 342 аудиоцифровой, 344 беспроводный, 78 видео, 341

гальваническая развязка, 15 ИPNP, 323 клавиатуры, 311 монитора, 326 мыши, 316 НГМД, 353,354 параллельный, 13

Centronics, 321

LPT-порт, 17 последовательный, 13

MIDI 345

RS-232C, 49

асинхронный, 59

инфракрасный, 78

принтеров, 324

токовая петля, 57

управление потоком, 61 принтеров и плоттеров, 320 телефония, 415 токовая петля, 57 топология, 14 устройства хранения, 394 интерфейсная карта, 410 интерфейсные кабели, 39 инфракрасная связь, 78 ИPNP, 323

524

Алфавитный указатель

кабели, 39

Fire Wire, 106

IDE ATA, 363

MIDI, 345

SCSI, 120

STP, 406

USB, 88,89,333

UTP, 108

и разъемы, IEEE 1284, 40

интерфейса НГМД, 355

интерфейсные, 39

монитора, 326

нуль-модемные, 70

питания, 505

принтера, 323 кабельная выборка, 387 каналы ATA, 383 карта

AGP, 212

CompactFlash, 396

ISA, 44,81

ММС, 400

PC Card 81228

PCI, 18,81

PCMClf 228,399

SD, 400

SmartMedia Card, 399

прототип, 146 квитирование, 60 клавиатура, 311

Alt-набор, 485

ASCII-коды, 485

Int09h 316

Intl6h, 316,483,484,493

Int9h, 483,484,493

буфер 483

интерфейс, 311 программный, 484

область в BDA, 483

прерывания, 483

разъемы XT, AT, PS/2, 311

расширенный ASCII-код, 485

скан-код, 310

коммутатор Fibre Channel, 141 коммутируемая линия, 414 компрессия, 30,34 контроллер

DMA 8237, 465 .

FDCAT, 356

PCI IDE, 384

НГМД

программирование, 356 регистры, 357

прерываний 8259А, 456

конфигурирование, 44,89

АТА, 387

СОМ-порта, 70

jumperless, 414

LPT-порта, 44

SCSI, 134,142

адаптеров Ethernet, 414 ISA, 164 концентратор Fibre Channel, 141

Л

линейный интерфейс SCSI, 116 линия телефонная коммутируемая, 414

м

манипулятор, 70

маршрутизатор Fibre Channel, 141 маскируемые прерывания, 458 монитор, 341 мост

Fibre Channel, 141

PCI, 198

главный, 198

одноранговый, 198 мышь, 70

н

накопители

внешние, 43

дисковые, 24

подключение, 43 НГМД

интерфейс, 353,354

контроллер, 356

программирование, 356

регистры контроллера, 357

£ежим" з56

скорость передачи данных, 356

смена носителя, 354 немаскируемое прерывание, 457

обмен

дуплексный, 14

полудуплексный, 14

симплексный, 14

обработка аппаратного прерывания, 459

одноранговый мост, 198

ООД, 49 . ,

п

память

DDR SDRAM, 244 DRAM, 235

Алфавитный указатель

525

память (продолжение) NVRAM, 277 RDRAM, 245 SDRAM, 240

инициализация, 245

команды, 240

латентность, 241 SIPP, 256

адаптеры модулей, 254 верхняя, 454 виртуальная, 470 время доступа, 236 динамическая, 235

BEDO, 240

EDO, 239

FPM, 238

асинхронная, 238

временные параметры, 236

модули, 251

синхронная, 240 маркировка модулей, 254 модули

DIMM, 261

DIMM-184, 267

DRAM cards, 274

ECC, 253

RIMM, 269

SIMM-30, 257

SIMM-72, 258

SIPP 257

SO DIMM-144, 272

SODIMM-72, 271

без паритета, 252

двусторонние, 257

идентификация, 254,255

односторонние, 257

организация контроля, 252

с паритетом, 252

с фиктивным паритетом, 252

со встроенной коррекцией, 253 регенерация, 238

CBR, 238

ROR, 238

автономная, 238

без импульса CAS, 238

скрытая, 238 с интерфейсом

I2C, 308

SPI, 309

с последовательными интерфейсами, 305 средства энергосбережения, 242,249 статическая, 274

асинхронная, 274

синхронная пакетная, 275 физическая, 454

память (продолжение) энергонезависимая, 276 EEPROM, 277,282 EPROM, 277,280 FRAM, 277 PROM, 277 UV-EPROM, 277 масочная, 278

однократно программируемая, 278 программаторы, 279 программирование, 276 репрограммируемая, 278 стирание EPROM, 279 фЛЭШ1

282

параллельный интерфейс, 13 Centronics, 321 SCSI 116 подключение

адаптеров ЛВС, 43 накопителей, 43 сканера, 43 полубайтный ввод, 23 полубайтный обмен, 23 полудуплексный обмен, 14 последовательный интерфейс, 13,49,59,78 поток данных, 60 прерывания ISA, 461 LPT-порта, 20 NMI, 457 PCI, 460

аппаратные, 20,457,459,481 клавиатуры, 483 конфигурирование, 460 конфликты, 463 ложные, 461 маскируемые, 458 мультипроцессорных систем, 461 разделяемые, 462 таблица назначений, 459 чувствительность, 461 процессор х86, 468 прямое управление шиной, 411,465 прямой доступ к памяти, 463,465

развязка

гальваническая, 15,510

конденсаторная, 511

оптическая, 510

трансформаторная, 511 разъемы

ATА, 363

СОМ-порта, 52

526

Алфавитный указатель

разъемы (продолжение)

DFP, 337

DVI, 337

EVC. 333

FireWire, 107

Game-порта, 349

LPT-порта, 42,43

MIDI, 346

P&D, 336

P&D-А, 333,336

RCA, 341

RS-232C, 52

SCSI, 121

USB, 89

VAFC, 326

VFC, 326

аудио, 342

блока питания ATX, 514

видео, 334

клавиатуры XT, AT, PS/2, 311

НГМД, 354

питания

накопителей, 513 системной платы, 513 расширения LPT-порта, 21 режим

DMAATA, 377

большой реальный, 471

передачи АТА, 376 РЮ, 376

стандартный реальный, 471

сброс

счетчика, 494

таймера, 495

флага, 494

связь через LPT-порт, 42 сектор, 360 сетевой фильтр, 506 сжатие, 34

симплексный обмен, 14 системный таймер, 476 сканер, 43

скорость передачи данных, 55 слот

AGP, 219

AGP Pro, 221

ISA, 27,44,137

PC Card, 228,229

PCI, 113,137

PCMCIA, 145

Small PCI, 234 средства измерения времени, 476

таймер

CMOS RTC, 477

системная поддержка, 478,494

системный, 476

трехканалышй, 476 телефония

автоматическое определение номера, 417

блокиратор, 417

импульсный набор, 416

интерфейс, 415

параметры сигналов, 418

тональный набор, 416 телефонная линия, 414 телефонный аппарат, 415 терминаторы SCSI, 125 тестирование, 45

СОМ-порта, 73

LPT-порта, 45 токовая петля, 57,58 топология соединения, 14 трансляция

геометрии, 490 трекбол, 70 трехканальный счетчик-таймер, 476

управление SCSI, 142 потоком, 369

аппаратное RTS/CTS, 61 варианты, 60 посылка уведомления, 61 программное XON/XOFF, 62 энергопотреблением, 93,332 устройства защиты, 307

фиксированный диск, 486 флэш-память, 282

boot block, 284,293

bulk erase, 284,291

data polling, 301

flash file, 284,296

NAND, 285

NOR, 285

PCMCIA, 291

smart voltage, 300

toggle bit, 301

архитектура

асимметричная, 284 симметричная, 284

корпуса, обозначение, 286

Алфавитный указатель

флэш-память (продолжение) назначение

выводов, 287

сигналов, 288 с интерфейсом

DRAM, 286

LPC, 286

с синхронным интерфейсом, 285 сектарированная, 293 фирмы

AMD, 301

Intel, 283

хост-адаптер, 141 ATA, 360 SCSI, 141

ш

шина

ACCESS.Bus, 427 CardBus, 229 Compact PCI, 196 EISA, 146,148,151 IEEE 1394, 106 ISA, 146

каналы DMA, 147 прерывания, 147

шина (продолжение)

пространство памяти, 147

распределение ресурсов, 147

сигналы, 149

слот, 148 Mini PCI, 196 Miniature Card, 229 PC Card, 228,229 PC/104, 161 PCI, 175

автоконфигурирование, 204

команды, 185

мост, 198

слот, 193 PCI-X, 196 PCMCIA, 228 PXI, 197

SCSI, 114,134,142 Small PCI, 196 SMBus, 433 USB, 88 расширения, 145,146

электропитание заземление, 506

оборудования локальных сетей, 510 сетевой фильтр, 506

Аналоговые интерфейсы

Аналоговые интерфейсы позволяют подключать стандартную бытовую аппаратуру, микрофон, аналоговой выход CD-ROM. На большинстве карт массового потребления для аналоговых сигналов применяют малогабаритные разъемы — «мини-джеки» (jack) диаметром 3,5 мм, моно и стерео. Эти разъемы универсальны (используются на бытовой аппаратуре), но имеют весьма низкое качество контактов — они являются источником шумов (шорохов и тресков), а также иногда

8.5. Интерфейсы аудиоустройств_______________________________________ 343

просто теряют контакт. Их полноразмерные 6-миллиметровые «родственники», характерные для профессиональной аппаратуры, имеют весьма высокое качество, но из-за крупных габаритов на звуковых картах не используются. На некоторых высококачественных картах сигналы линейного входа и выхода выводятся на пары разъемов RCA, которые обеспечивают очень хороший контакт, особенно в позолоченном варианте. В просторечии такие разъемы, часто используемые на бытовых видеомагнитофонах, называют «колокольчиками» или «тюльпанами».

Раскладка цепей на мини-джеках унифицирована: левый канал — на центральном контакте, экран (земля) на внешнем цилиндре, правый канал — на промежуточном цилиндре. Если стереоджек включить в моногнездо и наоборот, сигнал пойдет только по левому каналу. Все соединения в стереосистемах осуществляются «прямыми» кабелями (контакты разъемов соединяются «один в один»). Для подключения центрального и низкочастотного каналов в 6-колоночной системе единого подхода нет — может потребоваться перекрестный кабель. Неправильное подключение будет заметно по «писку» низкочастотной колонки (сабвуфера) и «бубнению» центральной колонки.

Подключение к звуковой карте устройств через внешние разъемы проблем обычно не вызывает — они унифицированы, и достаточно знать назначение разъемов, маркированных на задней панели.

¦ Line In — линейный вход от магнитофона, тюнера, проигрывателя, синтезатора и т. п. Чувствительность порядка 0,1-0,3 В.

¦ Line Out — линейный выход сигнала на внешний усилитель или магнитофон, уровень сигнала порядка 0,1-0,3 В.

¦ Speaker Out — выход на акустические системы или головные телефоны. Подключать к нему внешний усилитель мощности нецелесообразно, поскольку здесь искажения больше, чем на линейном выходе.

¦ Мгс In — микрофонный вход, чувствительность 3-10 мВ. Этот вход обычно монофонический, но иногда используется трехконтактное гнездо (как в стерео), у которого дополнительный контакт (на месте правого канала) выделен для подачи питания на электретный микрофон.

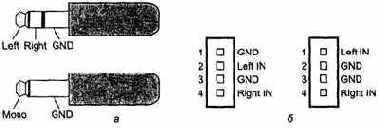

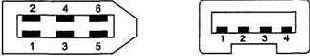

Подключение внутренних устройств к аналоговым входам может доставить больше забот. Для этого используются четырехштырьковые разъемы, различающиеся как шагом межу выводами, так и их назначением. Для подключения CD-ROM часто ставят рядом два, а то и три разъема с параллельно соединенными сигнальными контактами, но и это может не помочь, если кабель имеет другое расположение сигналов. Спасти может перестановка контактов на разъеме кабеля, для чего иголкой нажимают на фиксирующий выступ контакта. После этого контакт можно вытянуть в сторону кабеля и переставить в другое гнездо. Вид и варианты расположения сигнальных контактов аудиовходов приведены на рис. 8.15. Для полноты картины добавим, что разъем может иметь ключ с противоположной стороны (по ошибке сборщика кабеля или по внутреннему стандарту его производителя). Задача подключения все-таки не безнадежна, поскольку требует правильной расстановки только двух сигнальных контактов, а контакты общего провода выделя-

344

Глава 8. Специализированные интерфейсы периферийных устройств

ются тем, что на плате соединяются с шиной, а на кабеле — с экраном. Положение левого и правого каналов аудио-CD в большинстве случаев не так уж и важно.

Рис. 8.15. Разъемы подключения аудиосигналов

Аналоговые интерфейсы RGB

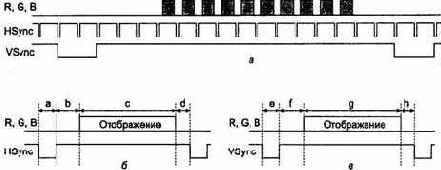

Интерфейс RGB Analog с аналоговой передачей сигналов яркости базисных цветов позволяет передавать формально неограниченное число оттенков. Сигналы базисных цветов в современных адаптерах формируются 8-разрядными ЦАП, что позволяет выводить 16,7 миллионов цветов (True Color). Для уменьшения перекрестных помех эти сигналы передаются по витым парам, с собственными обратными линиями (Return). Для согласования с кабелем в мониторе каждая сигнальная пара нагружается резистором. Черному цвету соответствует нулевой потенциал на линиях всех цветов, полной яркости каждого цвета соответствует уровень +0,7 В (не все графические адаптеры обеспечивают полную амплитуду сигнала). Сигналы управления, состояния и синхронизации передаются сигналами ТТЛ. Временные диаграммы интерфейса RGB (они применимы и к интерфейсу RGB TTL) иллюстрирует рис. 8.9. Сигналы R, G, В, здесь показаны условно — изображены интервалы, во время которых сигналы отображаются засветкой точек экрана (видимая часть изображения — в областях пересечения отображения по кадру и по строке, в остальное время луч принудительно гасится). На рисунке показаны основные временные параметры сигналов. Стандарт VESA DMT (Discrete Monitor Timing, 1994-1998 гг.) задает дискретный ряд вариантов параметров для различных режимов разрешения. Несколько более поздний стандарт VESA GTF (Generalized Timing Formula Standard) задает формулы для определения всех параметров синхронизации, исходными данными для расчета являются следующие:

¦ формат экрана в пикселах (например, 800x600);

¦ необходимость дополнительного видимого обрамления (overscan borders);

¦ тип развертки — построчная (non-interlaced) или черезстрочная (interlaced);

¦ одна из заданных частот: кадров, строк или пикселов.

Поскольку стандартов много, один и тот же набор этих параметров разными графическими картами и их драйверами может использовать несколько отличающи-

328

Глава 8. Специализированные интерфейсы периферийных устройств

еся ^ временные параметры сигнала. Эти вариации приходится компенсировать настройками монитора (размер и смещение по вертикали и горизонтали). Примеры параметров синхронизации для построчной развертки приведены в табл. 8.6. Обратим внимание, что для строчной развертки параметры синхронизации задаются в микросекундах, а для кадровой — в числе строк за это время.

Рис. 8.9. Временные диаграммы интерфейса RGB: a — общая картина, б — строчная развертка, в — кадровая развертка

Таблица 8.6. Параметры синхронизации

8.4. Интерфейсы графических адаптеров

329

VESA кадров, строк, пикселов, развертка, мкс развертка,

ГЦ кГц МГц строк

Fv Fh Fp Abcdefgh

|

1280x1024 |

75.0 |

79.9 |

135 |

|

SXGA(75Hz) |

|||

|

1280x1024 |

85.0 |

91.1 |

|

|

SXGA(85Hz) |

|||

|

1600x1024 |

60.0 |

63.6 |

|

|

(60Hz) |

|||

|

1600x1024 |

85.0 |

91.4 |

|

|

(85Hz) |

|||

|

1600x1200 |

85.0 |

106.3 |

|

|

(85Hz) |

|||

|

1920x1200 |

60.0 |

74.5 |

|

|

(60Hz) |

|||

|

1920x1200 |

85.0 |

107.1 |

|

|

(85Hz) |

|||

|

2048x1536 |

75.0 |

120.2 |

|

|

(75Hz) |

|||

|

2304x1440 |

80.0 |

120.6 |

|

|

(80Hz) |

В адаптере PGA используется совмещенная синхронизация (Composite Sync) сигналом (H+V)Sync.; этот режим поддерживают и многие современные мониторы.

Таблица 8.7. Аналоговый интерфейс монитора PGA (разъем DB-9S)

Сигнал

|

||

|

|

1 |

Red |

|

2 |

Green |

|

3 |

Blue |

|

4 |

(H+V)Sync |

|

5 |

Mode Control |

|

6 |

Red Return |

|

7 |

Green Return |

|

8 |

Blue Return |

|

9 |

GND |

|

330 |

1 Сигналы DDC Return, SDA и SCL задействуются только при поддержке DDC. При этом контакт 9 может использоваться для питания логики DDC (+5 В).

2 Сигнал (H+V)Sync используется при совмещенной синхронизации (Composite Sync).

Таблица 8.9. Переходник 9-15 аналогового интерфейса монитора

Контактов 15

|

1 |

Red |

1 |

|

2 |

Green |

2 |

|

3 |

Blue |

3 |

|

4 |

H.Sync |

13 |

|

5 |

V.Sync |

14 |

|

6 |

Red Return |

6 |

|

7 |

Green Return |

7 |

|

8 |

Blue Return |

8 |

|

9 |

GND |

10,11 |

В компьютерах Macintosh монитор, совместимый по параметрам с VGA, имеет разъем DB-15P (такой же, как и у Game-порта PC). Назначение его выводов приведено в табл. 8.10.

8.4. Интерфейсы графических адаптеров___________________________________________ 331

Таблица 8.10. Разъем VGA Macintosh Контакт Сигнал

|

1 |

Red Return |

|

2 |

Red |

|

3 |

Comp.Sync |

|

4 |

IDO |

|

5 |

Green |

|

6 |

Green Return |

|

7 |

ID1 |

|

8 |

He используется |

|

9 |

Blue |

|

10 |

ID2 |

|

11 |

Sync. GND |

|

12 |

V.Sync |

|

13 |

Blue Return |

|

14 |

H.SyncGND |

|

15 |

H.Sync |

Кроме передачи изображения, по интерфейсу передают информацию, необходимую для автоматизации согласования параметров и режимов монитора и компьютера. «Интересы» компьютера представляет дисплейный адаптер, к которому и подключается монитор. С его помощью обеспечиваются идентификация монитора, необходимая для поддержки PnP, и управление энергопотреблением монитора.

Для простейшей идентификации в интерфейс ввели четыре логических сигнала IDO-ID3, по которым адаптер мог определить тип подключенного монитора IBM. Со стороны монитора эти линии либо подключались к шине GND, либо оставлялись неподключенными. Однако из этой системы идентификации использовали лишь сигнал ID1, по которому определяют факт подключения монохромного монитора. Монохромный монитор может быть опознан адаптером и иначе — по отсутствию нагрузки на линиях Red и Blue.

Параллельную идентификацию мониторов заменила последовательная по каналу цифрового интерфейса VESA DDC (Display Data Channel). Этот канал построен на интерфейсах PC (DDC2B) или ACCESS.Bus (DDC2AB), которые требуют всего два ТТЛ-сигнала SCL и SDA. Интерфейс DDC1 является однонаправленным — монитор посылает адаптеру блок своих параметров по линии SDA (контакт 12), которые синхронизируются сигналом V.Sync (контакт 14). На время приема блока параметров адаптер может повысить частоту V.Sync до 25 кГц (генератор кадровой развертки по такой высокой частоте синхронизироваться не будет). Интерфейс DDC2 является двунаправленным; для синхронизации используется выделенный сигнал SCL (контакт 15). Интерфейс DDC2AB отличается тем, что допускает подключение ПУ, не требующих высокой скорости обмена, к компьютеру по последовательной шине ACCESS.Bus (см. п. 11.1.2).

332_________ Глава 8. Специализированные интерфейсы периферийных устройств

Блок параметров расширенной идентификации дисплея EDID (Extended Display Identification) имеет одну и ту же структуру для любой реализации DDC (табл. 8.11).

Таблица 8.11. Блок расширенной идентификации EDID Смещение,байт Длина,байт Назначение

|

0 |

8 |

|

8 |

10 |

|

18 |

2 |

|

20 |

15 |

|

35 |

19 |

|

54 |

72 |

|

126 |

1 |

|

127 г |

1 |

Идентификатор изделия (назначается производителем)

Версия EDID

Основные параметры и возможности дисплея

Установленные параметры синхронизации

Дескрипторы параметров синхронизации (байты 4-18)

Флаг расширения

Контрольная сумма

Таблица 8.12. Управление энергопотреблением монитора (VESA DPMS)

Режим H.Sync V.Sync

Standby Неактивен Активен

Suspend Активен Неактивен

Off Неактивен Неактивен

¦ 3 разъема — сигналы базисных цветов, смешанная синхронизация (composite sync) передается в канале зеленого цвета;

¦ 4 разъема — смешанная синхронизация передается по отдельному кабелю;

¦ 5 разъемов — вертикальная и горизонтальная синхронизация передается по раздельным кабелям.

С помощью коаксиальных кабелей возможно удаление монитора от компьютера на расстояние до 10-15 м при хорошем изображении.

8.4. Интерфейсы графических адаптеров

333

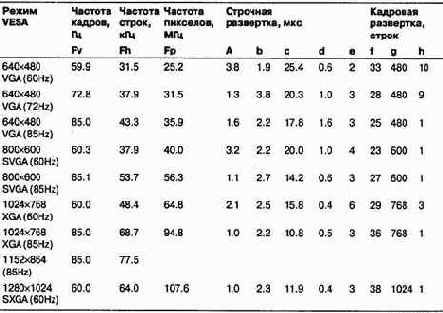

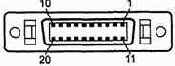

Для расширения частотного диапазона (и учитывая тенденцию к использованию последовательных шин USB и Fire Wire) для подключения ПУ к системному блоку компьютера VESA в 1995 г. предложила новый тип разъема EVC (Enhanced Video Connector). В 1998 г. была принята новая редакция, и разъем переименован в P&D-A (Plug&Display-Analog) с небольшими изменениями, касающимися резервных контактов и цепей питания зарядного устройства. Кроме обычного аналогового интерфейса RGB и канала DDC2, разъем P&D-A (EVC) имеет контакты для видеовхода, входные и выходные стереоаудиосигналы, шины USB и Fire Wire, а также линии питания постоянного тока для зарядки аккумуляторов портативных ПК. Разъем имеет две секции: высокочастотную для присоединения четырех коаксиальных кабелей и низкочастотную на 30 контактов (рис. 8.10, табл. 8.13). Контакты высокочастотной секции, хотя и не являются коаксиальными, позволяют передавать сигналы с частотами до 2 ГГц. Контактом экранов является крестообразная перегородка. При использовании 75-омных коаксиальных кабелей на частоте 500 МГц гарантируется уровень отражений и перекрестных помех не выше 2 %. Высокочастотная секция — контакты С1-С4 и С5 (экран) — требуется для передачи цветовых сигналов R, G, В и синхросигнала пикселов РХ Clock. Синхросигнал пикселов «интересен» матричным дисплеям (с их цифровой природой), его использование позволяет уменьшить погрешности передачи видеоинформации. Частота этого сигнала равна либо частоте сканирования пикселов, либо ее половине (на высокой частоте нужна двойная синхронизация, по фронту и спаду, что уравнивает требования к полосе пропускания для линий цветовых данных и линии синхронизации пикселов).

Таблица 8.13. Разъем P&D-A (EVC)

|

Контакт |

Цепь |

Контакт |

Цепь |

Контакт |

Цепь |

|

1 |

Audio Output, Right |

11 |

Charging power input, + |

21 |

Audio input, left |

|

2 |

Audio Output, Left |

12 |

Charging power input, - |

22 |

Audio input, right |

|

3 |

Audio Output, Return |

13 |

Video input, Y или composite in |

23 |

Audio input, return |

|

4 |

Sync Return |

14 |

Video input, return |

24 |

Stereo sync (TTL) |

|

5 |

Horizontal Sync (TTL) |

15 |

Video input, С in |

25 |

DDC return |

|

6 |

Vertical Sync (TTL) |

16 |

USB Data + |

26 |

DDC Data (SDA) |

|

7 |

Резерв |

17 |

USB Data - |

27 |

DDC Clock (SCL) |

|

8 |

Резерв |

18 |

USB/1394 common mode shield |

28 |

+5 В |

|

9 |

1394TPA- |

19 |

1394VG |

29 |

1394TPB+ |

|

10 |

1394TPA+ |

20 |

1394VP |

30 |

1394TPB- |

|

С1 |

R (аналог.) |

C3 |

PX Clock |

||

|

С2 |

G (аналог.) |

C5 |

GND (для R, G, B) |

C4 |

В (аналог.) |

334

Глава 8. Специализированные интерфейсы периферийных устройств

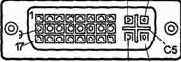

Рис. 8.10. Разъем Б/С и P&D (розетка)

Разъем поделен на компактные зоны для каждой группы сигналов, правда, шины USB и 1394 используют общий контакт для экрана. Назначение контактов видеовхода (S-Video или композитный, PAL или NTSC) может программироваться по каналу DDC2.

Стандарт определяет три уровня реализации: базовый, мультимедийный и полный. Базовый включает только видеосигналы и DDC, в мультимедийном должны быть аудиосигналы. При использовании коннектора в полном объеме монитор превращается в коммутационный центр, который соединяется с компьютером одним кабелем, а все остальные ПУ (включая клавиатуру, мышь, принтер) подключаются к монитору. Разъем может использоваться для подключения портативного ПК к док-станции. EVC собирает сигналы от разных подсистем — графической, видео, аудио, последовательных шин и питания. Этот общий разъем, устанавливаемый на корпусе системного блока, может соединяться с разными платами внутренними кабелями через промежуточные разъемы. Этот разъем не следует путать с похожим по виду и названию разъемом P&D-A/D, описанным в следующем пункте. Разъемы EVC на компьютерах встречаются нечасто, и это объясняется не только их довольно высокой ценой. Устанавливать EVC на графическую карту неудобно (она «обрастет» лишними интерфейсными шлейфами), а интегрированные системные платы редко имеют графические адаптеры с выдающимися параметрами, для которых он нужен.

Аппаратные прерывания

Аппаратные прерывания обеспечивают реакцию процессора на события, происходящие асинхронно по отношению к исполняемому программному коду. Прерывания в процессорах х86 подробно рассмотрены в литературе [6,7]. Здесь напомним, что аппаратные прерывания делятся на маскируемые и немаскируемые. На немаскируемое прерывание (NMI) процессор реагирует всегда (если обслуживание предыдущего NMI завершено); этому прерыванию соответствует фиксированный вектор 2. Немаскируемые прерывания в PC используются для сигнализации о фатальных аппаратных ошибках. Сигнал на линию NMI приходит от схем контроля паритета памяти, от линий контроля шины ISA (IOCHK) или шины PCI (SERR#). Сигнал NMI блокируется до входа процессора установкой в 1 бита 7 порта 070h, отдельные источники разрешаются и идентифицируются битами порта 061h:

¦ бит 2 R/W — ERP — разрешение контроля ОЗУ и сигнала SERR# шины PCI;

¦ бит 3 R/W — EIC — разрешение контроля шины ISA;

¦ бит 6 R — IOCHK — ошибка контроля на шине ISA (сигнал ЮСНК#);

¦ бит 7 R — РСК — ошибка четности ОЗУ или сигнал SERR* на шине PCI.

458 Глава 12. Архитектурные компоненты IBM PC-совместимого компьютера

Реакция процессора на маскируемые прерывания может быть задержана сбросом его внутреннего флага IF (инструкции СLI — запретить прерывания, STI — разрешить). По возникновении события, требующего реакции, адаптер (контроллер) устройства формирует запрос прерывания, который поступает на вход контроллера прерываний. Контроллер прерываний формирует общий запрос маскируемого прерывания для процессора, а когда процессор подтверждает этот запрос, контроллер сообщает процессору вектор прерывания, по которому выбирается программная процедура обработки прерываний. Процедура должна выполнить действия по обслуживанию данного устройства, включая сброс его запроса для обеспечения возможности реакции на следующие события и посылку команды завершения в контроллер прерываний.

Вызывая процедуру обработки, процессор автоматически сохраняет в стеке значение всех флагов и сбрасывает флаг IF, что запрещает маскируемые прерывания. При возврате из процедуры (по инструкции I RET) процессор восстанавливает сохраненные флаги, в том числе и установленный IF, что снова разрешает прерывания. Если во время работы обработчика прерываний требуется реакция на иные прерывания (более приоритетные), то в обработчике должна присутствовать инструкция STI. Особенно это касается длинных обработчиков; здесь инструкция STI должна вводиться как можно раньше, сразу после критической (не допускающей прерываний) секции. Следующие прерывания того же или более низкого уровня приоритета контроллер прерываний будет обслуживать только после получения команды завершения прерывания EOI (End Of Interrupt).

Маскируемые прерывания используются для сигнализации о событиях в устройствах. Обработка сигналов запросов прерывания выполняется контроллером прерываний, программно совместимым с 8259А. Контроллер прерываний позволяет маскировать отдельные входы запросов и организовывать систему приоритетов запросов от различных входов. В машинах класса AT применяется каскадное соединение двух контроллеров. Ведущий контроллер 8259А#1 обслуживает запросы О, 1, 3-7; его выход подключается к входу запроса прерываний процессора. К его входу 2 подключен ведомый контроллер 8259А#2, который обслуживает запросы 8-15. При этом поддерживается вложенность приоритетов — запросы 8-15 со своим рядом убывающих приоритетов вклиниваются между запросами 1 и 3 ведущего контроллера, приоритеты запросов которого также убывают с ростом номера. В XT каскадирование не применялось, и один контроллер 8259А обслуживал все 8 линий запросов.

Контроллер прерываний 18259А подробно описан в литературе [1, 7]; здесь приведем лишь необходимые сведения, в большинстве случаев достаточные для работы. Контроллеры расположены по адресам 20-21h (8259A#1) и AO-Alh (8259A#2), обращаться к ним следует как к однобайтным портам ввода-вывода.

После инициализации (процедурой POST и при загрузке ОС) все неиспользуемые входы контроллеров замаскированы (на запросы прерываний реагировать не будут), а их векторы прерываний указывают на «заглушку» — процедуру с единственной инструкцией IRET. Первым делом программа должна загрузить в память свой обработчик и подставить указатель на его начало в соответствующее место таблицы прерываний. Далее следует размаскировать вход, для чего выполняется чтение регистра маски (адрес 21h для 8259А#1, Alh для 8259А#2), обнуление соответ-

12.3. Аппаратные прерывания

459

ствующего бита (см. табл. 12.2) и запись в регистр нового значения маски. При работе с контроллером прерываний от программы требуется лишь управление маской своего запроса (при инициализации программы нужно обнулить маску требуемого запроса) и корректное завершение обработки прерываний. Каждая процедура обработки аппаратного прерывания должна завершаться командой ЕОI (End Of Interruption), посылаемой контроллеру:

¦ для 1-го контроллера — посылка байта 20h по адресу 20h;

¦ для 2-го контроллера — посылка байта 2Oh по адресу AOh (EOI для ведомого

контроллера), затем посылка байта 20h по адресу 20h (EOI для ведущего кон

троллера).

Некорректно завершенная процедура не позволит повторно использовать данный или другие запросы прерываний. Если обработчик прерывания удаляется из памяти, предварительно должен быть замаскирован соответствующий ему вход контроллера. Все изменения в таблице прерываний должны выполняться при замаскированных прерываниях, чтобы избежать попытки использования вектора в процессе его модификации (это приведет к «вылету» программы).

На входы контроллеров прерываний поступают запросы от системных устройств (клавиатура, системный таймер, CMOS-таймер, сопроцессор), периферийных контроллеров системной платы и от карт расширения. Традиционно все линии запросов, не занятые перечисленными устройствами, присутствуют на всех слотах шины ISA/EISA.

Эти линии обозначаются как IRQx и имеют общепринятое назначение (табл. 12.2). Часть этих линий отдается в распоряжение шины PCI. В таблице отражены и приоритеты прерываний — запросы расположены в порядке их убывания. Номера векторов, соответствующих линиям запросов контроллеров, система приоритетов и некоторые другие параметры задаются программно при инициализации контроллеров. Эти основные настройки остаются традиционными для обеспечения совместимости с программным обеспечением.

Таблица 12.2. Аппаратные прерывания (в порядке убывания приоритета)

|

Имя (номер1) |

Вектор |

Контроллер/маска |

Описание |

|

NMI |

02h |

Контроль канала, паритет |

|

|

(в XT — сопроцессор) |

|||

|

IRQO |

08h |

#1/1h |

Таймер (канал £8253/8254) |

|

IRQ1 |

09h |

#1/2h |

Клавиатура |

|

IRQ2 |

OAh |

#1/4h |

XT — резерв, AT — недоступно |

|

(подключается каскад IRQ8-IRQ15) |

|||

|

IRQ8 |

70h |

#2/1 h |

CMOS RTC — часы реального времени |

|

IRQ9 |

71h |

#2/2h |

Резерв |

|

IRQ10 |

72h |

#2/4h |

Резерв |

|

IRQ11 |

73h |

#2/8h |

Резерв |

|

IRQ12 |

74h |

#2/10h |

PS/2-Mouse (резерв) |

|

IRQ 13 |

75h |

#2/20h |

Математический сопроцессор |

460______ Глава 12. Архитектурные компоненты IBM PC-совместимого компьютера

Таблица 12.2 (продолжение)

|

IRQ14 |

76h |

#2/40h |

HOC — контроллер НЖМД |

|

IRQ15 |

77h |

#2/80h |

Резерв |

|

IRQ3 |

OBh |

#1/4h |

COM2, COM4 |

|

IRQ4 |

OCh |

#1/10h |

COM1,COM3 |

|

IRQ5 |

ODh |

#1/20h |

XT — HOC, AT — LPT2, Sound (резерв) |

|

IRQ6 |

OEh |

#1/40h |

FDC — контроллер НГМД |

|

IRQ7 |

OFh |

#1/80h |

LPT1 — принтер |

Для запросов прерывания с шины PCI используются 4 линии запросов прерывания, которые обозначают как INTR А, В, С, D. Эти линии работают по низкому уровню, что дает возможность их разделения (совместного использования).

Линии циклически сдвигаются в слотах и независимо коммутируются на доступные линии IRQx с помощью конфигурационных регистров чипсета. Линии IRQx, используемые шиной PCI, становятся недоступными для шины ISA. «Дележку» линий между шинами, а также управление чувствительностью отдельных линий обеспечивают параметры CMOS Setup, а также система PnP.В параметрах ISA или Legacy подразумевают использование линий IRQx традиционными адаптерами шины ISA (статическое распределение), a PCI/PnP — использование адаптерами шины PCI или адаптерами PnP для шины ISA (динамическое распределение). Общая схема формирования запросов прерываний изображена на рис. 12.1.

Каждому устройству, для поддержки работы которого требуются прерывания, должен быть назначен свой номер прерывания. Назначения номеров прерываний выполняются с двух сторон: во-первых, адаптер, нуждающийся в прерываниях,

12.3. Аппаратные прерывания_________________________________________ 461

должен быть сконфигурирован на использование конкретной линии шины (джам-перами или программно). Во-вторых, программное обеспечение, поддерживающее данный адаптер, должно быть проинформировано о номере используемого вектора. В процессе назначения прерываний может участвовать система PnP для шин ISA и PCI, для распределения линий запросов между шинами служат специальные параметры CMOS Setup.

Контроллер прерываний позволяет программировать свои входы на чувствительность к уровню или перепаду сигнала.

¦ Чувствительность к уровню (level sensitive) означает, что контроллер прерываний вырабатывает запрос прерывания процессора по факту обнаружения определенного уровня (на ISA — высокого) на входе DRQx. Если к моменту завершения обработки этого запроса (после записи команды EOI в регистр контроллера прерываний) контроллер снова обнаруживает активный уровень на том же входе DRQx, то он снова сформирует запрос на прерывание процессора.

¦ Чувствительность к перепаду (edge sensitive) означает, что контроллер прерываний вырабатывает запрос прерывания процессора только по факту обнаружения перепада (на ISA — положительного) на входе DRQx.

Повторно запрос по этому входу возможен только по следующему такому же перепаду, то есть сигнал предварительно должен вернуться в исходное состояние.

В любом случае сигнал запроса аппаратного прерывания IRQx должен удерживаться генерирующей его схемой, по крайней мере, до цикла подтверждения прерывания процессором. В противном случае источник прерывания корректно идентифицирован не будет, и контроллер сообщит ложный вектор прерывания (spurious interrupt), соответствующий его входу с максимальным номером (IRQ7 для первого контроллера и IRQ 15 для второго). Обычно адаптеры строят так, что сигнал запроса сбрасывается при обращении программы обслуживания прерывания к соответствующим регистрам адаптера.

В шине ISA прерывание вырабатывается по положительному перепаду сигнала на линии запроса. Это плохо по двум причинам: такой способ подачи сигнала, во-первых, имеет меньшую помехозащищенность, чем срабатывание по отрицательному перепаду, во-вторых, отрезает путь к нормальному разделению линий запросов (см. ниже), для которого полностью пригоден способ подачи сигнала по низкому уровню. Поскольку традиционный контроллер позволяет задавать чувствительность — уровень (Level) или перепад (Edge) — только для всех входов одновременно, в общем случае разделяемые прерывания на шине ISA вместе с корректной работой системных устройств использоваться не могут.

На современных системных платах функции контроллеров прерываний возлагаются на чипсет, который может иметь и более гибкие возможности управления, чем пара контроллеров 8259А. В операционном режиме всегда сохраняется программная совместимость с 8259А. Процедура инициализации контроллеров может и отличаться от традиционной, но ею занимается тест POST, который «знает» особенности системной платы. В симметричных мультипроцессорных системах аппаратные прерывания работают сложнее, поскольку их могут обслуживать различные процессоры. Для реализаций системы прерываний процессоры Pentium и выше имеют встроенный контроллер прерываний APIC (Advanced Programmable

462 Глава 12. Архитектурные компоненты IBM PC-совместимого компьютера

Interruption Controller). Внутренние контроллеры процессоров связаны между собой по шине APIC, к которой подключена и «ответная часть» чипсета, преобразующая запросы аппаратных прерываний в сигналы протокола APIC. В операционном режиме такая связка также совместима с 8259 А.

Аппаратные средства измерения времени

В IBM PC/AT имеются аппаратные средства для измерения времени. Трехканалъ-ный счетчик-таймер, программно совместимый с 18254 (в XT — 8253), выполняет следующие функции:

¦ канал 0: — генерация аппаратных прерываний (IRQO) каждые 54,936 мс (частота 18,206 Гц), вызывающих инкремент системного таймера (счетчика в ячейке 40:006Е BIOS Data Area);

¦ канал 1 — генерация запросов на регенерацию памяти;

¦ канал 2 — генерация звуковых сигналов или измерение времени.

Внутренние счетчики микросхемы имеют разрядность 16 бит, но общение с ними возможно только 8-битными операциями. При этом можно задавать значение только младшего байта счетчика (LSB), только старшего (MSB) или обоих (LSB/MSB), причем сначала передается младший, а потом старший байт. Программирование микросхемы осуществляется записью байт в управляющий регистр по отдельности для каждого канала. Назначение регистров счетчиков-таймеров приведено в табл. 12.5. Входная частота для всех каналов 1,19318 МГц. Штатно все каналы работают в режиме генерации импульсов. Счет для каналов 0 и 1 разрешен постоянно. В канале 2 используется управляющий вход GATE, разрешающий счет, который управляется битом О (T2G, R/W) системного порта AT (061h). Выходной сигнал канала 2 может быть программно считан (Т20, бит 5 того же порта). При использовании канала 2 для измерения времени необходимо отключить формирование звука (обнулив бит SPK, R/W, бит 1 порта 061h).

Таблица 12,.5. Регистры счетчиков-таймеров Порт, R/W Назначение

равна 0 (соответствует коэффициенту деления 65 536)

041 RW Счетчик 1 — регенерация памяти. Режим 010, LSB, Binary, константа счетчика

равна 12h (18)

042 RW Счетчик 2 — генератор звука, измерение времени. Вход GATE от бита 0 порта

В 8255 (061). Режим 011, LSB/MSB, Binary, значение счетчика определяет высоту тона

12.6. Аппаратные средства измерения времени____________________________ 477

Порт, R/W Назначение_____________________________________________________________

043 W Управляющий регистр. Биты 7,6 — выбор счетчика 0,1,2. Биты 5,4 — режим

, обращения: 00 — защелка текущего значения; 01 — LSB — только младший байт; 10 — MSB — только старший байт; 11 — LSB/MSB — сначала младший, затем старший байты. Биты 3-1 — режим счетчика: 000 — прерывание по счетчику; 001 — ждущий мультивибратор (одновибратор, у 8254 несколько отличается от 8253); х10 — генератор коротких импульсов заданной частоты; х11 — генератор меандра; 100 — счетчик событий с разрешением; 101 —счетчиксобытий с перезапуском. Бит 0 —0=Bin (двоичный счет), 1 =BCD — (двоично-десятичный счет)

¦ часы-календарь (год, месяц, число, час, минута, секунда);

¦ будильник, подающий сигнал в назначенный час, минуту и секунду;

¦ генератор меандра, позволяющий формировать запросы прерываний с задан

ной частотой (как правило, 1024 Гц).

CMOS RTC является источником аппаратных прерываний (IRQ8). Прерывания могут возникать от будильника, генератора меандра и после смены времени в часах. Отдельные источники прерывания идентифицируются чтением ячейки ОСЬ и разрешаются записью в ячейку OBh.

Доступ к ячейкам CMOS RTC осуществляется через порты ввода-вывода 070h (индекс ячейки) и 071h (данные). Заметим, что бит 7 порта 70h используется и для блокировки NMI (см. п. 12.4), так что диапазон адресов памяти CMOS ограничен пределами 0-7Fh. Поскольку эта память имеет быстродействие порядка единиц микросекунд, между командами записи адреса и чтения-записи данных необходима программная задержка. Во время изменения состояния часов данные, считываемые из ячеек 0-9, могут оказаться некорректными.

Признаком этой ситуа ции является единичное значение бита 7 ячейки OAh. Для определения момента окончания смены состояния часов можно пользоваться и разрешением соответствующего источника прерывания. Назначение ячеек CMOS RTC, относящихся к таймерной части, приведено в табл. 12.6 (полное определение ячеек см. в [1]).

Таблица 12.6. Назначение ячеек таймерной части CMOS RTC Индекс Назначение

(37 в PS/2) 02 — минуты; 03 — минуты будильника; 04 — часы; 05 — часы будильника; 06 — день недели; 07 — день месяца; 08 — месяц; 09 — год (2 младшие цифры); 32h — век-1 (2 старшие цифры года); 37h — век-1 (2 старшие цифры года) в PS/2

478______ Глава 12. Архитектурные компоненты IBM PC-совместимого компьютера

Таблица 12.6 (продолжение) Индекс Назначение

(О — готов к чтению); биты [6:4] — делитель частоты (для кварца на 32,768 кГц — 010); биты [3:0] — 0110 — выходная частота меандра 1024 Гц

OBh PTC Status Register В (регистр статуса В): бит 7 — остановка часов

(О — нормальный ход); бит 6 — разрешение периодических прерываний (О — запрещено); бит 5 — разрешение прерывания от будильника (О — запрещено); бит 4 — разрешение прерывания по окончании смены времени (0 — запрещено); бит 3 (см. также регистр OAh) — разрешение выходного меандра (0 — запрещено); бит 2 — формат BCD/BIN (0 — BCD); бит 1 — 12/24-часовой режим (1 — 24-часовой); бит 0 — зимнее/летнее время (О — переключение запрещено)

OCh RTC Status Register С (регистр статуса С): чтение флагов идентификаторов

прерывания: бит 7 — IRQF (общий запрос прерывания); бит 6 — PF (периодические прерывания); бит 5 — AF (прерывание от будильника); бит 4 — UF (прерывание по окончании смены времени); биты [3:0] — зарезервированы

ODh RTC Status Register D (регистр статуса D): бит 7 — питание (1 — норма,

0 — разрядбатареи); биты [6:0] —зарезервированы

Функции BIOS Int 15 h позволяют с помощью CMOS RTC вводить задержку или запускать таймер установки флага (через заданное время установить бит 7 указанной ячейки памяти). Время задается в микросекундах, но минимальная выдержка зависит от производительности ПК (достижимы единицы миллисекунд), максимальная выдержка — около 70 часов.

Начиная с процессоров Pentium, появилась возможность измерения времени с точностью до такта ядра процессора. Для этого процессоры имеют внутренний 64-битный счетчик TSC (Time Stamp Counter), обнуляющийся по аппаратному сбросу (сигналом RESET*). Разрядность позволяет считать без переполнения в течение нескольких столетий. Для доступа к счетчику имеется специальная инструкция RDTSC, правда, установкой флага TSD в управляющем регистре CR4 (процессора) ОС может сделать ее привилегированной (доступной только на нулевом уровне привилегий). В этом случае приложение, исполняемое на уровне 3, может аварийно завершаться по отказу исполнения инструкции. ОС может и позволить обращение к этому регистру, но «подсовывая» программе угодное ей значение времени. Заметим, что из-за внутреннего умножения частоты в процессоре результат чтения счетчика может отставать от реального времени на число, достигающее коэффициента умножения частоты. Правда, такая точность никому и не нужна (она потеряется в измеряющих программах).

12.7. Способы запуска программ_____________________________________ 479

Аппаратный интерфейс

Все сигналы интерфейса НГМД являются логическими с уровнями ТТЛ, активный уровень — низкий. Формирователи выходных сигналов накопителя имеют выход типа «открытый коллектор». Интерфейс подразумевает наличие терминаторов — нагрузочных резисторов — для каждой сигнальной линии устройства. Теоретически их предполагалось включать только на последнем дисководе в шлейфе, практически же их никогда и не отключают. Современные трехдюймовые накопители используют «распределенный терминатор» — резисторы с относительно высоким сопротивлением (1-1,5 кОм), постоянно соединяющие входные линии интерфейса с шиной +5 В. Низкие частоты интерфейсных сигналов позволяют не задумываться о точности согласования импеданса шлейфа и сопротивления терминатора. Однако если на шлейфе стоят только старые 5"-накопители со снятыми терминаторами, они могут отказаться надежно работать (выходные линии с открытым коллектором останутся без нагрузки).

Логически интерфейс довольно прост. Для того чтобы заставить накопитель работать, его нужно выбрать сигналом Drive Sel и запустить мотор шпинделя сигналом Motor On. Для выборки накопитель имеет четыре сигнала DSO...DS3, но отзывается только на один из них, определенный установкой джамперов. Выбранный накопитель воспринимает управляющие сигналы от контроллера и передает контроллеру свои выходные сигналы. О том, что накопитель выбран, свидетельствует светодиодный индикатор на его лицевой панели.

Для перемещения головок на один шаг контроллер должен подать импульс Step; направление перемещения определяется уровнем сигнала Direction: при низком уровне (сигнал активен) перемещение происходит в сторону центра диска (номер трека увеличивается). Нулевой трек контроллер находит, перемещая головки от центра до появления сигнала Track 00. Выбор номера головки производится сигналом Side 1. Начало трека накопитель отмечает импульсом Index, который вырабатывается при прохождении индексного отверстия вращающейся дискеты мимо

354 ____________________________ Глава 9. Интерфейсы устройств хранения

датчика. Считываемые данные в закодированном (MFM) виде (но усиленные и сформированные в ТТЛ-сигнал) поступают от накопителя по линии Read Data. Для включения режима записи служит сигнал Write Gate, закодированные данные в цифровом виде поступают от контроллера по линии Write Data. Если установлена дискета, защищенная от записи, накопитель сообщит об этом сигналом Write Protect. Для снижения тока записи, которое требуется при работе накопителей HD с дискетами DD и QD, предназначен сигнал Reduce Write, его иное название — Low Current или FDHDIN. Для переключения головок на «вертикальную запись» (для дискет 2,88 Мбайт) служит сигнал FDEDIN. Оба эти сигнала вырабатываются контроллером, но для самого дисковода они дублируются сигналами от датчиков типа дискеты (сигнал FDEDIN необязателен, дисковод сам переключится по сигналу отдатчика). Некоторые модели дисководов позволяют изменить описанный способ работы датчиков типа дискеты, принятый для PC-совместимых ПК, — они могут быть отключены или выполнять информирование контроллера. Однако практически все кбн-троллеры сами управляют линиями интерфейса, соответствующими сигналам от этих датчиков. В этом управлении учитывается тип дисковода, описанный в CMOS Setup, и заказанный формат дискеты. Сигнал Reduce Write (низкий уровень) формируется контроллером при любом обращении к дисководу, описанному в CMOS как HD (High Density — высокая плотность, емкость 1,2 или 1,44 Мбайт), для работы с дискетами DD или QD (360 или 720 Кбайт). В некоторых контроллерах этот сигнал формировался, только когда контроллер настроен на скорость 300 Кбит/с (дискета 360/720 Кбайт в дисководе на 1,2 Мбайт). Такой контроллер может надежно форматировать и записывать дискеты 720 Кбайт в приводе на 1,44 Мбайт только при наличии правильно сконфигурированного датчика HD, иначе он все 3,5" дискеты будет записывать с высоким током записи, недопустимым для дискет QD.

Накопители HD при смене дискеты устанавливают сигнал Disk Changed, который сбрасывается после обращения к этому накопителю. Этот сигнал заслуживает особого внимания. Он имеется только у дисководов HD и ED (Extra High Density, малораспространенные дисководы на 2,88 Мбайт), причем способ использования этого контакта может определяться джамперами дисковода. В PC соответствующий джампер устанавливается в положение DC (Disk Change). Альтернативное использование этой линии — сигнализация готовности устройства, что может обозначаться как RY, RDY или SR, — для PC непригодно.

Заметим, что в интерфейсе нет никаких сигналов, прямо информирующих контроллер о готовности — наличии установленной дискеты. Контроллер может определить готовность, лишь выбрав накопитель и запустив мотор. Тогда отсутствие импульсов Index будет означать неготовность — нет дискеты или она не зафиксирована на шпинделе, или же не подключен дисковод (интерфейс или питание). Наличие дисковода контроллер может определить с помощью команды рекалибровки (см. ниже) — при ее выполнении дисковод должен подать сигнал TrackOO. Все НГМД, применяемые в PC, независимо от типа и размера имеют одинаковый интерфейс и унифицированные 34-контактные разъемы двух типов: с печатными двусторонними ламелями у устройств 5" и двухрядными штырьковыми контактами у устройств 3,5". Используемый в PC кабель-шлейф имеет перевернутый фрагмент из 7 проводов с номерами 10-16 (рис. 9.1). Этот поворот позволяет подключать к контроллеру одним шлейфом до двух НГМД, причем адрес накопителя.

9.1. Интерфейс НГМД

355

определяется его положением на шлейфе: для привода А: фрагмент перевернут, для В: — нет. Универсальный шлейф с пятью разъемами, изображенный на рисунке, позволяет подключать пару любых дисководов, которые должны располагаться в разных зонах шлейфа. Некоторые разъемы могут и отсутствовать, что сковывает свободу конфигурирования дисководов. В табл. 9.1 описан интерфейсный кабель с сигналами, приходящими на разные накопители.

Направление сигналов (I/O — ввод-вывод) указано относительно контроллера.

Рис. 9.1. Кабель интерфейса НГМД

Таблица 9.1. Кабель интерфейса НГМД

|

Контроллер |

ДисководВ: |

Дисковода: |

||||

|

Контакт1 |

Сигнал |

I/O |

Контакт1 Сигнал |

Контакт1 |

Сигнал |

|

|

2 |

FDHDIN (Reduce Write) |

О |

2 |

Low Current |

2 |

Low Current |

|

4 |

Резерв |

- |

4 |

Резерв |

4 |

Резерв |

|

6 |

FDEDEIN |

- |

6 |

FDEDIN (DS3) |

6 |

FDEDIN (DS3) |

|

8 |

Index |

I |

8 |

Index |

8 |

Index |

|

10 |

Motor On A |

о |

10 |

DSO |

16 |

Motor2 |

|

12 |

Drive Sel 1 |

о |

12 |

DS11 |

14 |

DS2 |

|

14 |

Drive Sel 0 |

о |

14 |

DS2 |

12 |

DS11 |

|

16 |

Motor On В |

о |

16 |

Motor2 |

10 |

DSO |

|

18 |

Direction |

о |

18 |

Direction |

18 |

Direction |

|

20 |

Step |

о |

20 |

Step |

20 |

Step |

|

22 |

Write Data |

о |

22 |

WData |

22 |

Wdata |

|

24 |

Write Gate |

о |

24 |

WGate |

24 |

Wgate |

|

26 |

Track 00 |

I |

26 |

ТВ 00 |

26 |

TROO |

|

28 |

Write Protect |

1 |

28 |

WProt |

28 |

WProt |

|

30 |

Read Data |

1 |

30 |

RData |

30 |

Rdata |

|

32 |

Side l |

о |

32 |

Sidel |

32 |

Side l |

|

343 |

Disk Changed |

1 |

343 |

DC |

34Э |

DC |

2 Пара сигналов, обеспечивающая выборку FDD (Motor On А и Drive Sel 0 для дисковода А: и Motor On

В и Drive Sel 1 для дисковода В:). 3 Контакт 34 в XT не используется.

356______________________________________ Глава 9. Интерфейсы устройств хранения

Контроллер НГМД и интерфейсный кабель, принятый в PC, позволяют адресоваться к одному из двух накопителей и включать мотор сигналами Drive Sel 0 и Motor On А для накопителя А: и Drive Sel 1 и Motor On В для накопителя В:. При этом на обоих накопителях джамперы устанавливаются так, что они отзываются на сигнал DS 1 (контакт 12 разъема). Обычно джамперы на дисководе обозначаются DSO / DS1 / DS2 / DS3, и следует установить джампер DS1.Если джамперы обозначаются как DS1 / DS2 / DS3 / DS4, что встречается нечасто, то следует установить DS2. Принятая система выборки позволяет все дисководы конфигурировать однотипно, а адрес задавать положением на шлейфе. В некоторых специфических клонах PC применяют иную систему выборки накопителей и «прямой» кабель-шлейф. При этом используется выборка устройства сигналом DS0, ко переключение выборки на эту линию некоторыми накопителями не поддерживается, в результате замена накопителей в этих «фирменных» машинах может стать хлопотным делом, особенно при отсутствии технической документации.

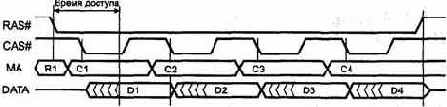

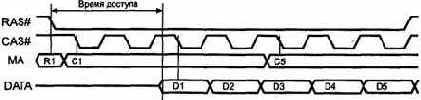

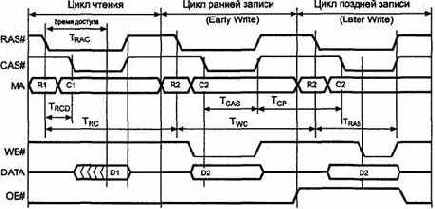

Асинхронная память — FPM, EDO и BEDO DRAM

Временная диаграмма, приведенная на рис. 7.1, может быть модифицирована для случая последовательного обращения к ячейкам, принадлежащим к одной строке матрицы. В этом случае адрес строки выставляется на шине только один раз и сигнал RAS# удерживается на низком уровне на время всех последующих циклов обращений, которые могут быть как циклами записи, так и чтения. Такой режим обращения называется режимом быстрого страничного обмена FPM (Fast Page Mode), или просто режимом страничного обмена (Page Mode), его временная диаграмма приведена на рис. 7.2. Понятие «страница» на самом деле относится к строке (row), а состояние с низким уровнем сигнала RAS# называется «открытой страницей». Преимущество данного режима заключается в экономии времени за счет исключения фазы выдачи адреса строки из циклов, следующих за первым, что позволяет повысить производительность памяти. Режим FPM поддерживает и самая обычная асинхронная память, называемая стандартной (Std).

Рис. 7.2. Страничный режим считывания стандартной памяти DRAM (FPM)

7.1. Динамическая память

239

Память EDO DRAM (Extended или Enhanced Data Out) содержит регистр-защелку (data latch) выходных данных, что обеспечивает некоторую конвейеризацию работы для повышения производительности при чтении. Регистр «прозрачен» при низком уровне сигнала CAS#, а по его подъему фиксирует текущее значение выходных данных до следующего его спада. Перевести выходные буферы в высоко-импедансное состояние можно либо подъемом сигнала ОЕ# (Output Enable), либо одновременным подъемом сигналов CAS# и RAS#, либо импульсом WE#, который при высоком уровне CAS# не вызывает записи (в PC управление по входу ОЕ# практически не используют).

Временная диаграмма работы с EDO-памятью в режиме страничного обмена приведена на рис. 7.3; этот режим иногда называют гиперстраничным режимом обмена НРМ (Hyper Page mode). Его отличие от стандартного заключается в подъеме импульса CAS# до появления действительных данных на выходе микросхемы.

Считывание выходных данных может производиться внешними схемами вплоть до спада следующего импульса CAS#, что позволяет экономить время за счет сокращения длительности импульса CAS#. Время цикла внутри страницы уменьшается, повышая производительность в страничном режиме на 40 %.

Рис. 7.3. Страничный режим считывания EDO DRAM (HPM)

Установка EDO DRAM вместо стандартной памяти в неприспособленные для этого системы может вызвать конфликты выходных буферов устройств, разделяющих с памятью общую шину данных. Скорее всего, этот конфликт возникнет с соседним банком памяти при чередовании банков. Для отключения выходных буферов EDO-памяти внутри страничного цикла обычно используют сигнал WE#, не вызывающий записи во время неактивной фазы CAS# (рис. 7.4, кривая а). По окончании цикла буферы отключаются лишь по снятию сигнала RAS# (рис. 7.4, кривая б).

Рис. 7.4. Управление выходным буфером EDO DRAM

240

Глава 7. Интерфейсы электронной памяти

Из принципиального различия в работе выходных буферов следует, что в одном банке не стоит смешивать EDO и стандартные модули. EDO-модули поддерживаются не всеми чипсетами и системными платами (в большей мере это относится к системным платам для процессоров 486).

В памяти BEDO DRAM (Burst EDO) кроме регистра-защелки выходных данных, стробируемого теперь по фронту импульса CAS#, содержится еще и внутренний счетчик адреса колонок для пакетного цикла. Это позволяет выставлять адрес колонки только в начале пакетного цикла (рис. 7.5), а во 2-й, 3-й и 4-й передачах импульсы CAS# только запрашивают очередные данные. В результате удлинения конвейера выходные данные как бы отстают на один такт сигнала CAS#, зато следующие данные появляются без тактов ожидания процессора, чем обеспечивается лучший цикл чтения. Задержка появления первых данных пакетного цикла окупается повышенной частотой приема последующих. BEDO-память применяется в модулях SIMM-72 и DIMM, но поддерживается далеко не всеми чипсетами.

Рис. 7.5. Страничный режим считывания BEDO DRAM

Вышеперечисленные типы памяти являются асинхронными по отношению к тактированию системной шины компьютера. Это означает, что все процессы инициируются только импульсами RAS# и CAS#, а завершаются через какой-то определенный (для данных микросхем) интервал. На время этих процессоров шина памяти оказывается занятой, причем в основном ожиданием данных.

Асинхронный режим передачи

Асинхронный режим передачи является байт-ориентированным (символьно-ориентированным): минимальная пересылаемая единица информации — один байт (один символ). Формат посылки байта иллюстрирует рис. 2.12. Передача каждого байта начинается со старт-бита, сигнализирующего приемнику о начале посылки, за которым следуют биты данных и, возможно, бит паритета (четности). Завершает посылку стоп-бит, гарантирующий паузу между посылками. Старт-бит следующего байта посылается в любой момент после стоп-бита, то есть между передачами возможны паузы произвольной длительности. Старт-бит, имеющий всегда строго определенное значение (логический 0), обеспечивает простой механизм синхронизации приемника по сигналу от передатчика. Подразумевается, что приемник и передатчик работают на одной скорости обмена. Внутренний генератор синхронизации приемника использует счетчик-делитель опорной частоты, обнуляемый в момент приема начала старт-бита. Этот счетчик генерирует внутренние стробы, по которым приемник фиксирует последующие принимаемые биты. В идеале стробы располагаются в середине битовых интервалов, что позволяет принимать данные и при незначительном рассогласовании скоростей приемника и передатчика. Очевидно, что при передаче 8 бит данных, одного контрольного и одного стоп-бита предельно допустимое рассогласование скоростей, при котором данные будут распознаны верно, не может превышать 5 %. С учетом фазовых искажений и дискретности работы внутреннего счетчика синхронизации реально допустимо меньшее отклонение частот. Чем меньше коэффициент деления опорной частоты внутреннего генератора (чем выше частота передачи), тем больше погрешность привязки стробов к середине битового интервала, и требования к согласованности частот становятся более строгие. Чем выше частота передачи, тем больше влияние искажений фронтов на фазу принимаемого сигнала.

60

Глава 2. Последовательный интерфейс — СОМ-порт

Взаимодействие этих факторов приводит к повышению требований к согласованности частот приемника и передатчика с ростом частоты обмена.

Рис. 2.12. Формат асинхронной передачи RS-232C

Формат асинхронной посылки позволяет выявлять возможные ошибки передачи.

¦ Если принят перепад, сигнализирующий о начале посылки, а по стробу старт-

бита зафиксирован уровень логической единицы, старт-бит считается ложным

и приемник снова переходит в состояние ожидания. Об этой ошибке прием

ник может не сообщать.

¦ Если во время, отведенное под стоп-бит, обнаружен уровень логического нуля,

фиксируется ошибка стоп-бита.

¦ Если применяется контроль четности, то после посылки бит данных передает

ся контрольный бит. Этот бит дополняет количество единичных бит данных

до четного или нечетного в зависимости от принятого соглашения. Прием бай